180 www.xilinx.com ChipScope Pro Software and Cores User Guide

UG029 (v14.3) October 16, 2012

Chapter 5: ChipScope Engine Tcl Interface

Returns

A bitfield containing the resulting status of the configuration. The bitfield can be logically

AND'ed with one or more of the following values to check the corresponding status

information:

$CSE_INTERNAL_DONE_HIGH_STATUS

$CSE_EXTERNAL_DONE_HIGH_STATUS

$CSE_CRC_ERROR_STATUS

$CSE_BITSTREAM_READ_ENABLED

$CSE_BITSTREAM_WRITE_ENABLED

An exception is thrown if the command fails.

Example

Configure the third device in the JTAG chain with the file mydesign.bit.

%set filename "mydesign.bit"

%set fp [open $filename r]

%fconfigure $fp -translation binary -blocking 1

%set fileData [read $fp]

%close $fp

%set configStatus [::chipscope::csefpga_configure_device $handle 2

"bit" $CSE_DEFAULT_OPTIONS $fileData [file size $filename]

"progressCallBack"]

Back to list of all CseFpga Tcl Commands

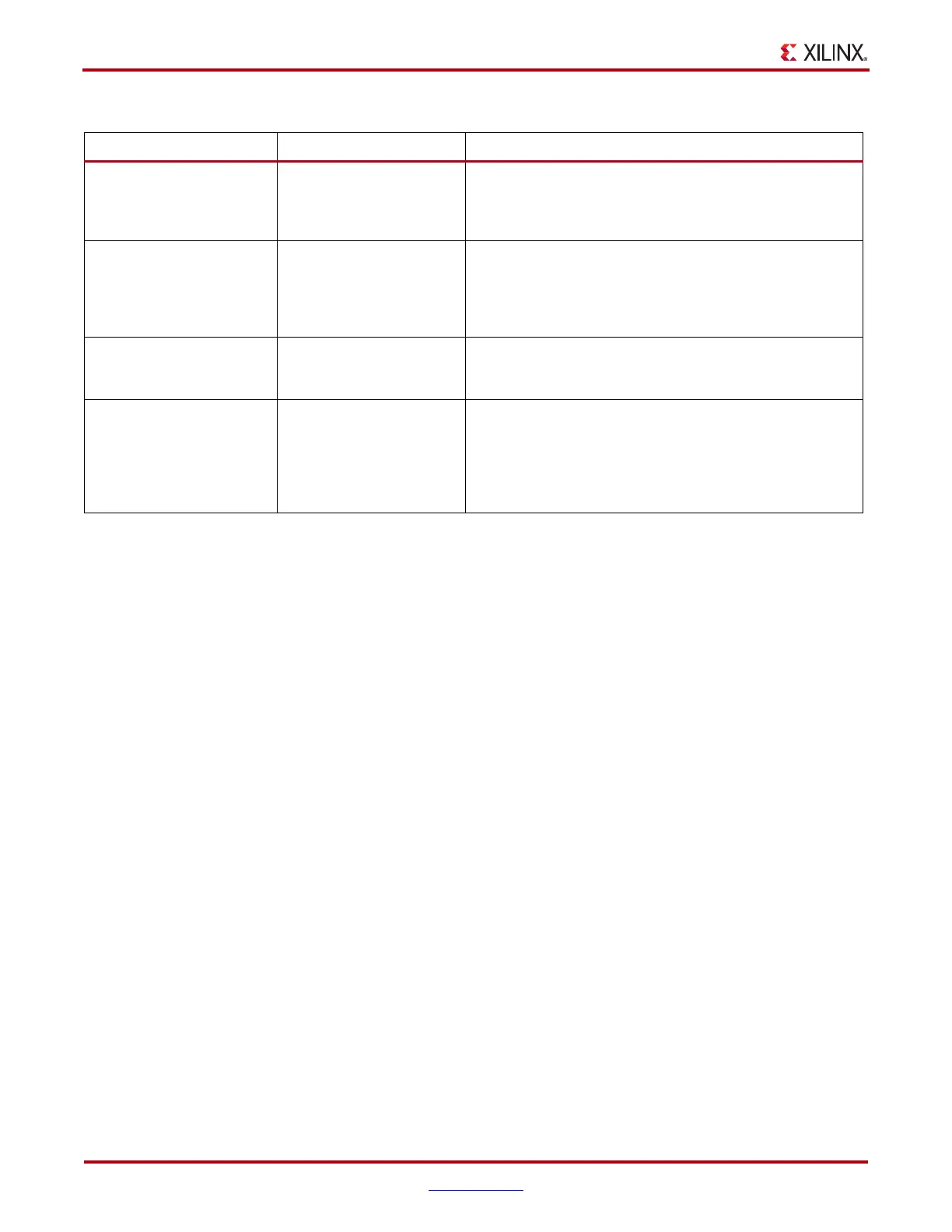

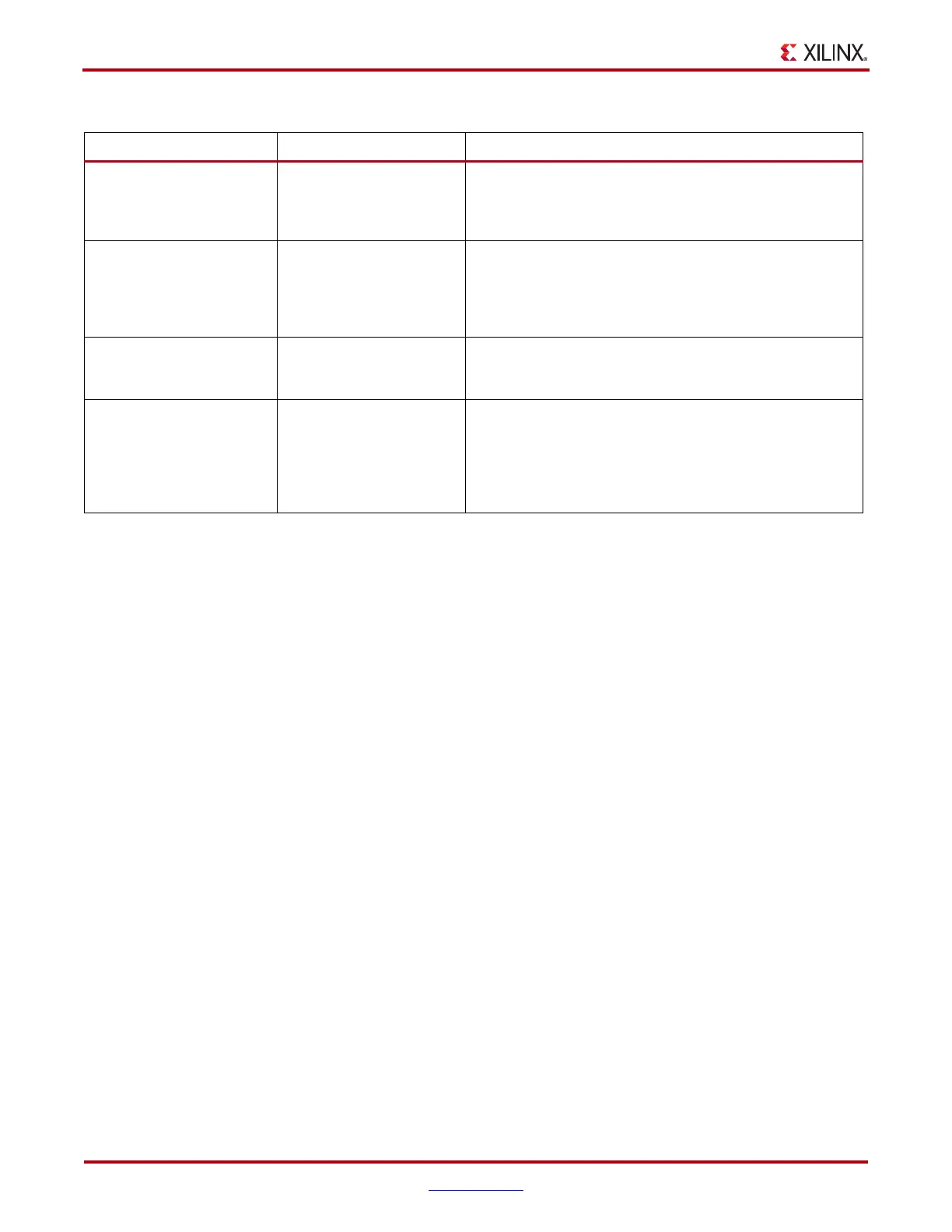

verify_internal_done verify_internal_done

=true,

verify_internal_done

=false

Read internal device DONE status after configuration from the

device JTAG instruction register. Default is

"verify_internal_done=true".

verify_external_done verify_external_done

=true,

verify_external_done

=false

Read external device DONE status after configuration from the

configuration status register. If you tie DONE device package

pins together, the DONE status is a logical AND of all device

DONE pins which have their DONE device package pins tied

together. Default is "verify_external_done=false".

verify_crc verify_crc=true,

verify_crc=false

Read CRC status after configuration from the device

configuration status register. Default is

"verify_crc=false".

use_assigned_config_

data

use_assigned_config_

data=true,

use_assigned_config_

data=false

Use the configuration and/or mask data provided by

::chipscope::csefpga_assign_config_data_to_de

vice or

::chipscope::csefpga_assign_config_data_file_

to_device. Default is

"use_assigned_config_data=false".

Table 5-47: Configuration Options (Cont’d)

Option Name Values Description

Loading...

Loading...