3-11

Performance Tests

PDH/DSn Internal Transmitter Clock Accuracy & Offset

Procedure

1 Recall the HP 37718A/19A DEFAULT SETTINGS as shown on Page 3-

4.

2 Connect the 75Ω OUT port of the PDH/DSn module to the Frequency

Counter. Terminate the Frequency Counter input in 75Ω (use the T

connector).

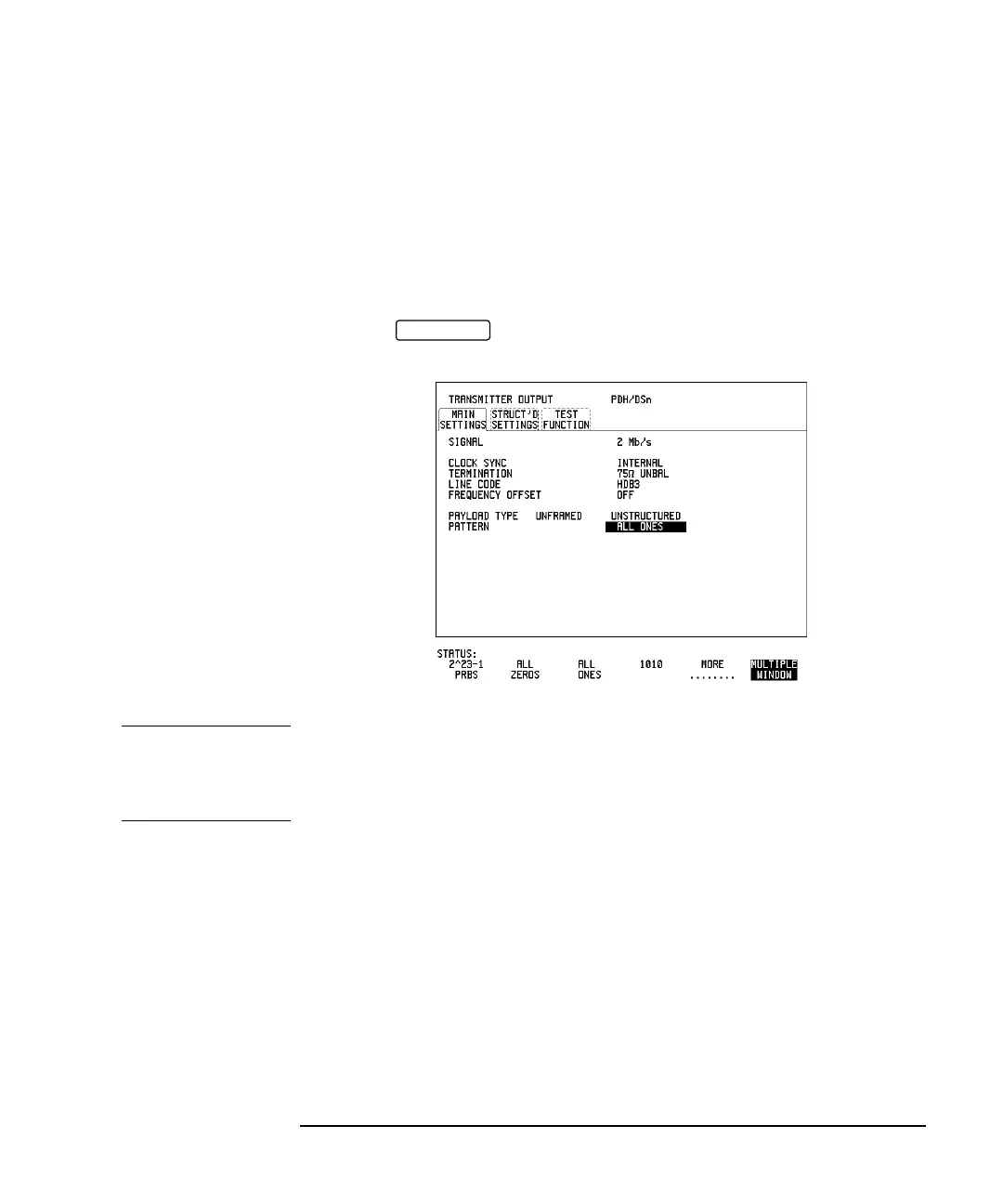

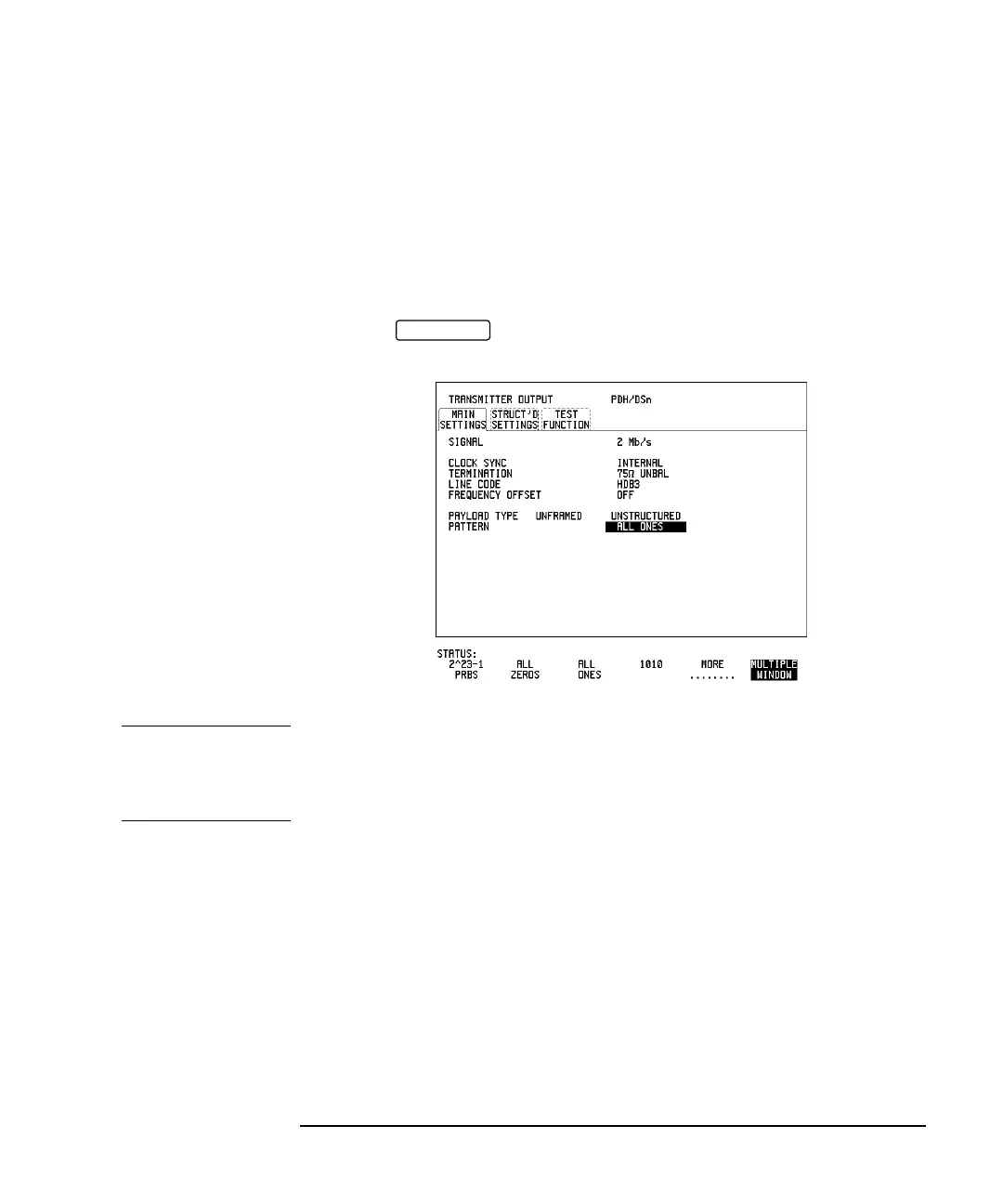

3 Set the display as shown opposite

NOTE When changing the PDH Rate or Offset value the VCXO takes time to

settle. As a consequence the frequency counter reading will not stabilize

until "VCXO OUTPUT BIT RATE SETTLING" clears from the STATUS

line of the display.

E1 (2.048Mb/s) Frequency Accuracy

4 Adjust the Frequency Counter ATTEN and Trigger Level to obtain a

stable reading and ensure that the frequency counter reading is

between 1023995Hz and 1024005Hz.

5 Select FREQUENCY OFFSET [+50PPM].

6 Adjust the Frequency Counter ATTEN and Trigger Level to obtain a

stable reading and ensure that the frequency counter reading is

between 1024046.5Hz and 1024055.5Hz.

TRANSMIT

Loading...

Loading...