Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 19 of 51

Jul.21.21

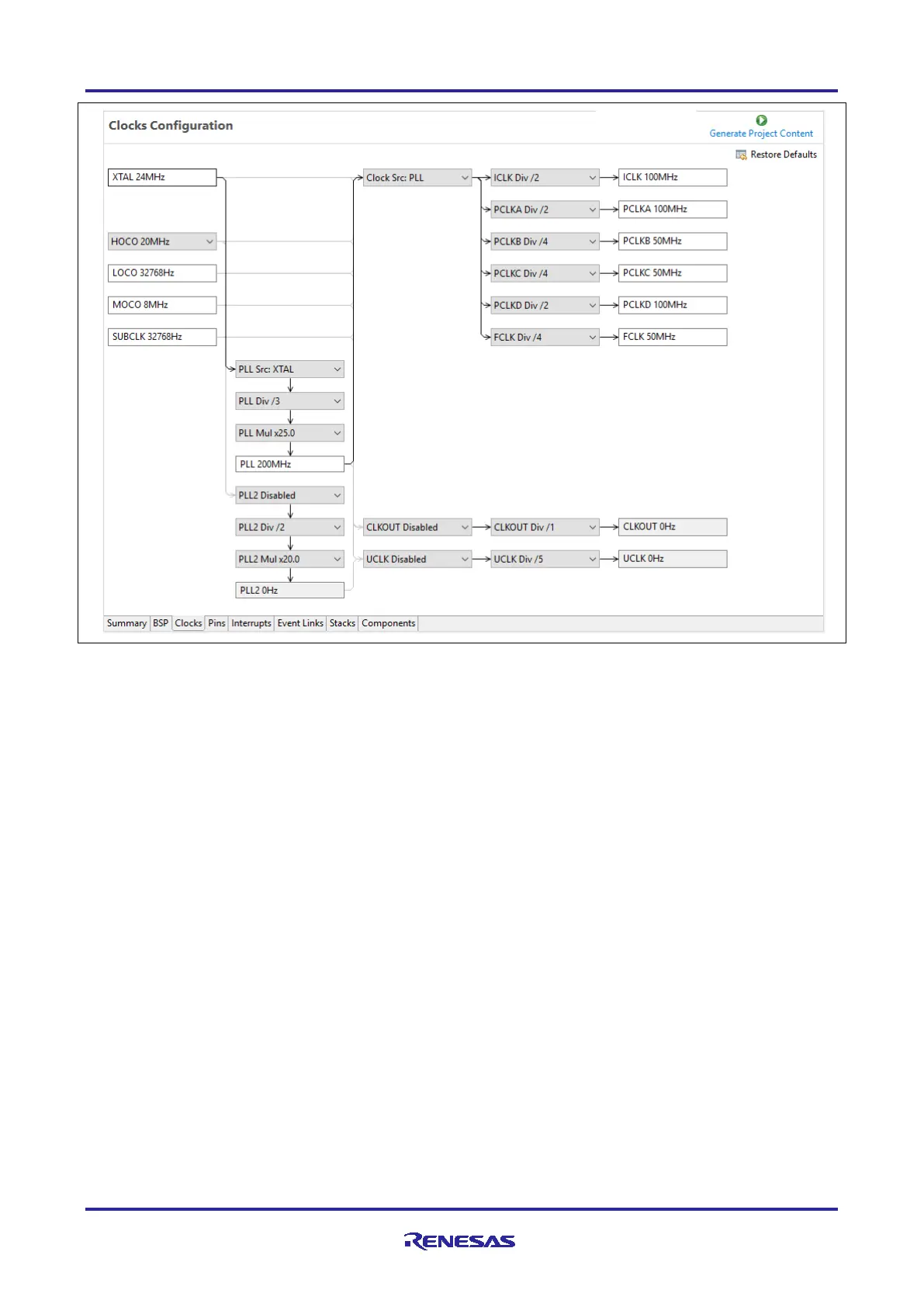

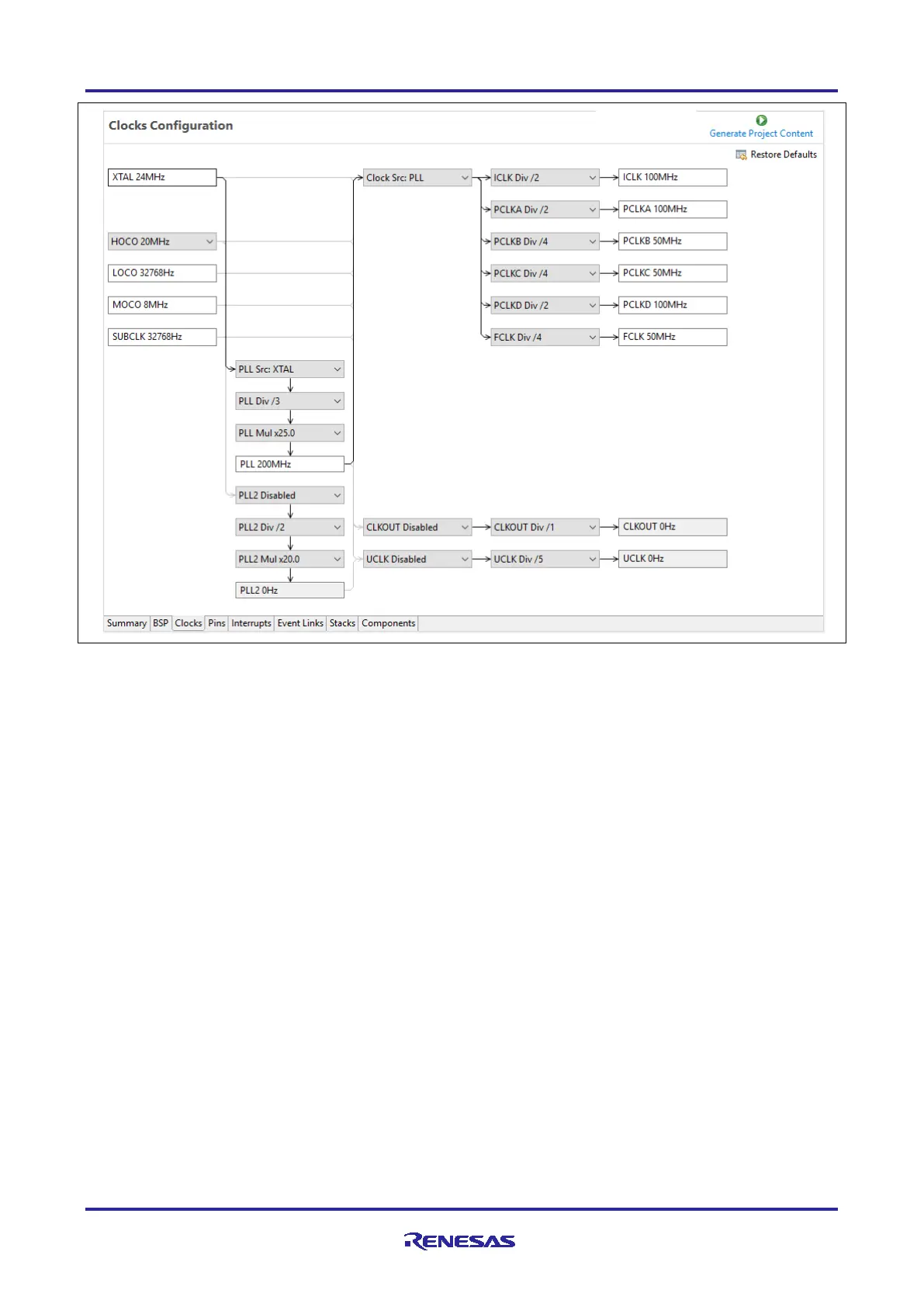

Figure 12. Clock Settings Using Renesas FSP Configurator

5.6 HOCO Accuracy

The internal high-speed on-chip oscillator (HOCO) runs at 16 MHz, 18 MHz, or 20 MHz for Arm Cortex-M33

core devices, and 24 MHz, 32 MHz, 48 MHz, or 64 MHz for Arm Cortex-M4 devices, with a typical accuracy

of +/-2% or better. HOCO accuracy specifications are characterized for various ambient operating

temperature (Ta) ranges.

For Arm Cortex-M33 devices, the accuracy of the HOCO may be improved by enabling the Frequency

Locked Loop (FLL) function, which results in a clock accuracy of +/-0.25% or better. Refer to the Electrical

Specifications in the hardware manual for details.

The HOCO may be used as an input to the PLL circuit. When the HOCO is used this way, no external

oscillator is required. This may be an advantage when space constraints, cost, or other limitations require a

reduced component count in a PCB design. However, there are performance tradeoffs and limitations due to

the clock accuracy which should be evaluated for your application.

5.7 Flash Interface Clock

The Flash interface Clock (FCLK) is used as the operating clock when programming and erasing internal

flash (ROM and DF) and for reading from the data flash. Therefore, the frequency setting of the FCLK will

have a direct impact on the amount of time it takes to read from the data flash. If the user’s program is

reading from the data flash, or performing programming or erasures on internal flash, then using the

maximum FCLK frequency is recommended.

The FCLK must run at a frequency of at least 4 MHz when writing or erasing code flash (ROM) or data flash.

Please note that the FCLK frequency does not have any impact upon reading from ROM or reading and

writing to RAM.

5.8 Board Design

Refer to the “Usage Notes” section of the Clock Generation Circuit (CGC) chapter in the Hardware User’s

Manual for more information on using the CGC and for board design recommendations.

Loading...

Loading...