Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 46 of 51

Jul.21.21

/* Open LPM driver and initialize LPM mode */

err = R_LPM_Open(&g_lpm_deep_sw_standby_ctrl, &g_lpm_deep_sw_standby_cfg);

/* Handle error */

if (FSP_SUCCESS != err)

{

return (err);

}

/* Transition to configured LPM mode: Deep Software Standby Mode */

err = R_LPM_LowPowerModeEnter(&g_lpm_deep_sw_standby_ctrl);

/* Handle error */

if (FSP_SUCCESS != err)

{

return (err);

}

Refer to the Application Notes "Getting Started with Low Power Applications" for RA devices for examples of

how to use FSP configurator and driver APIs for LPM.

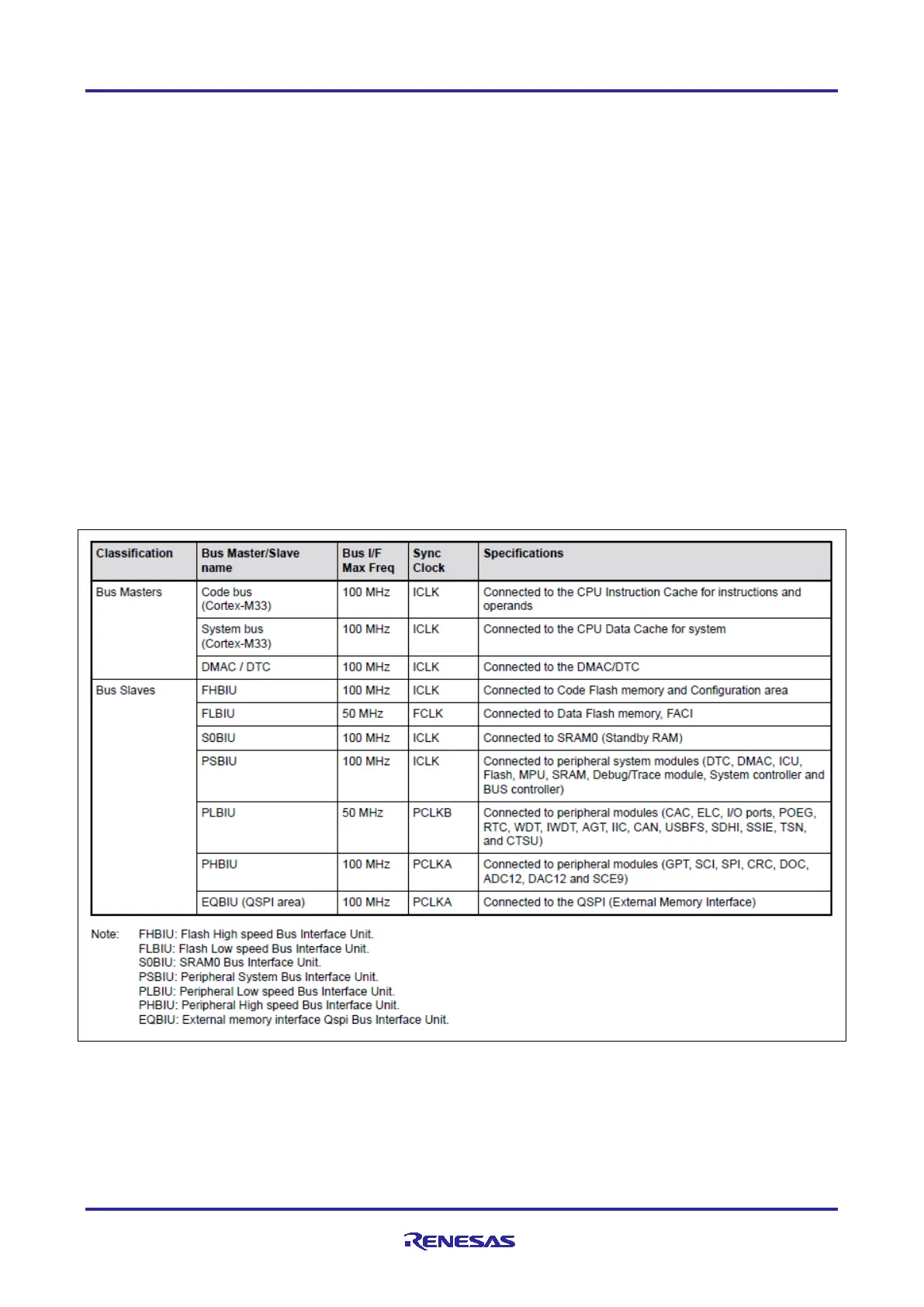

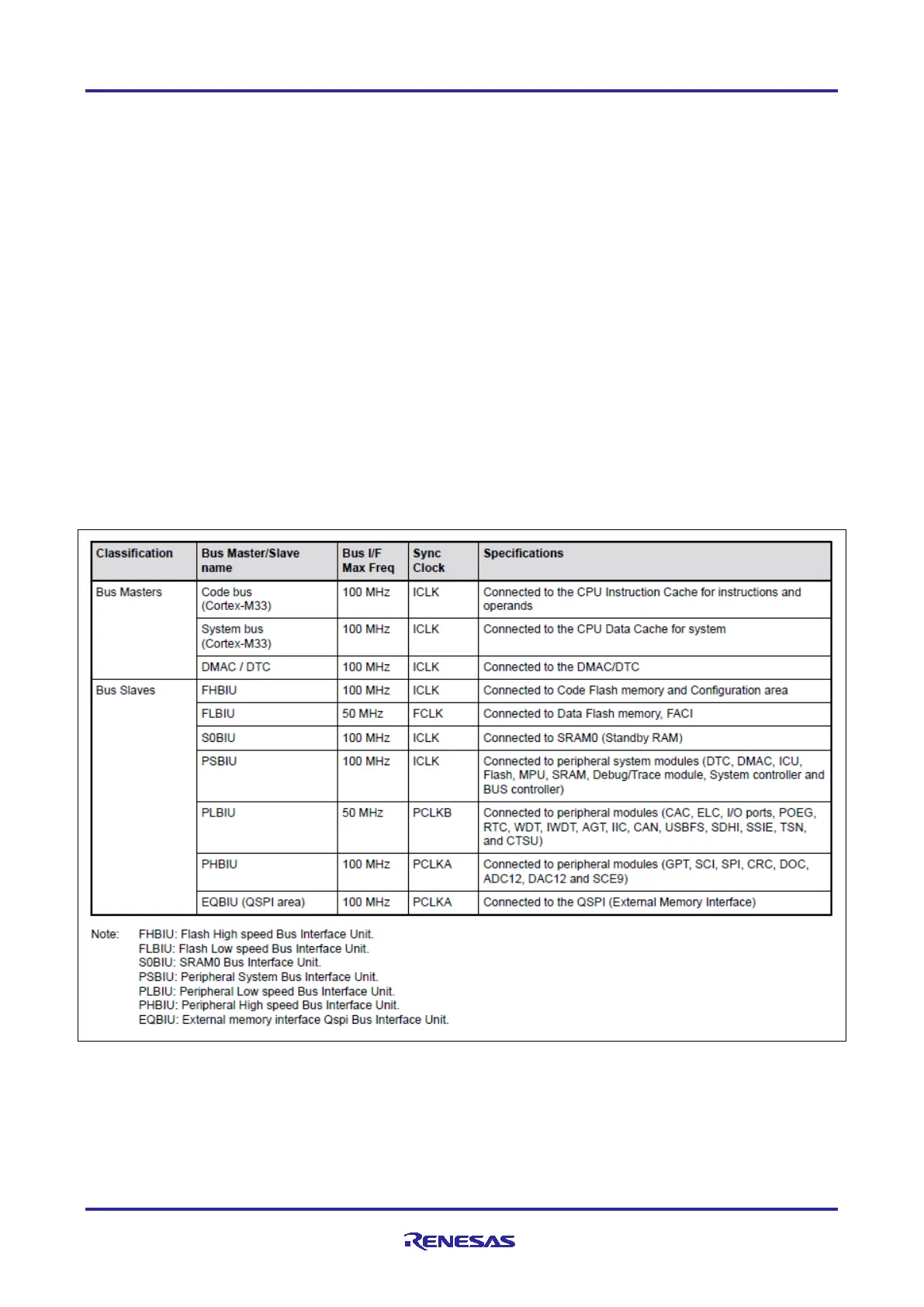

14. Buses

The buses in Arm Cortex-M33 MCU consist of a 32-bit AHB (Advanced High-performance Bus) bus matrix.

Figure 36 lists the bus masters and bus slaves and Figure 37 shows the bus configuration.

Note: Memory space is accessed in little-endian format when executing Arm Cortex instruction code.

Figure 36. RA4M3 Bus Specifications

Loading...

Loading...