Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 33 of 51

Jul.21.21

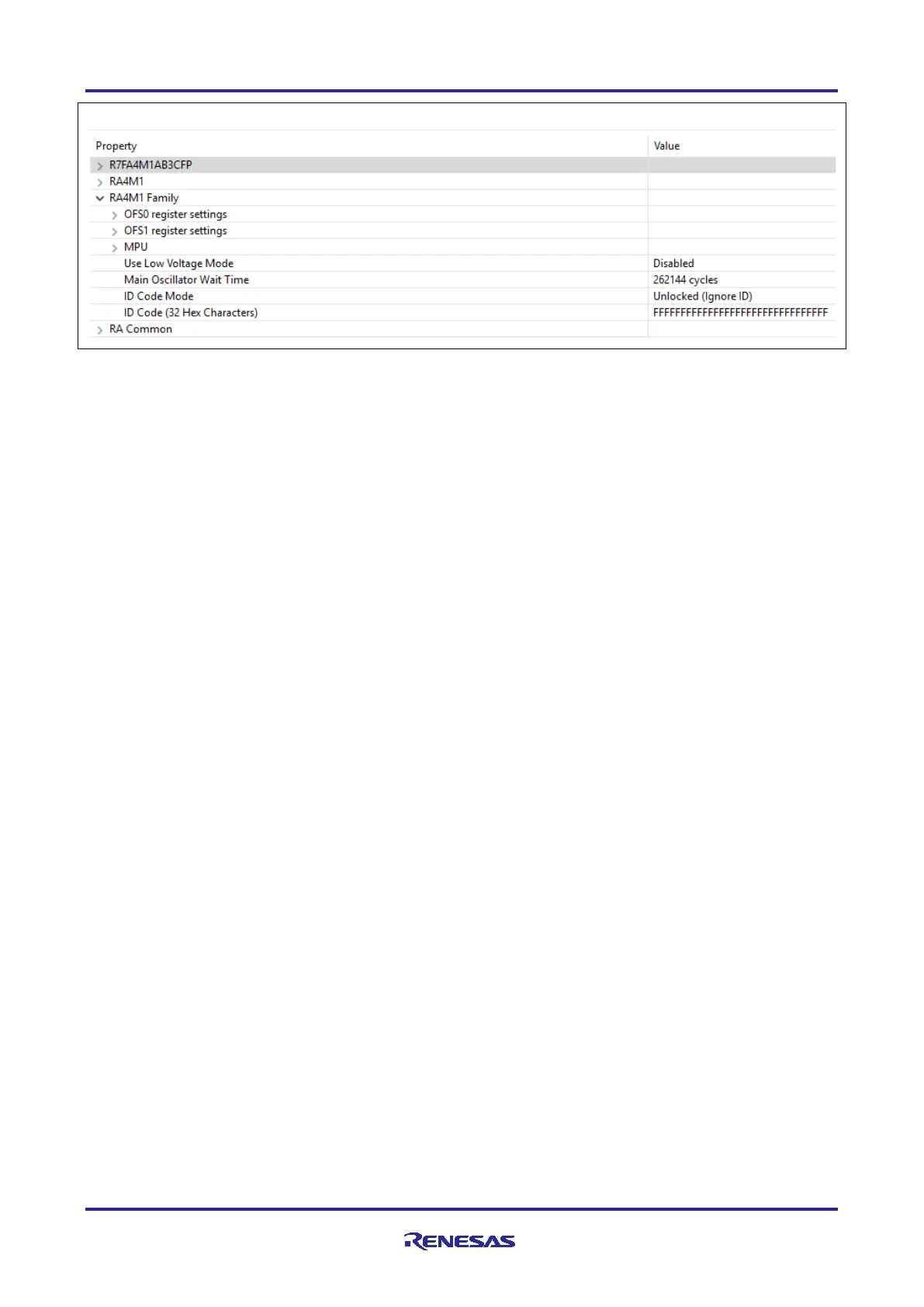

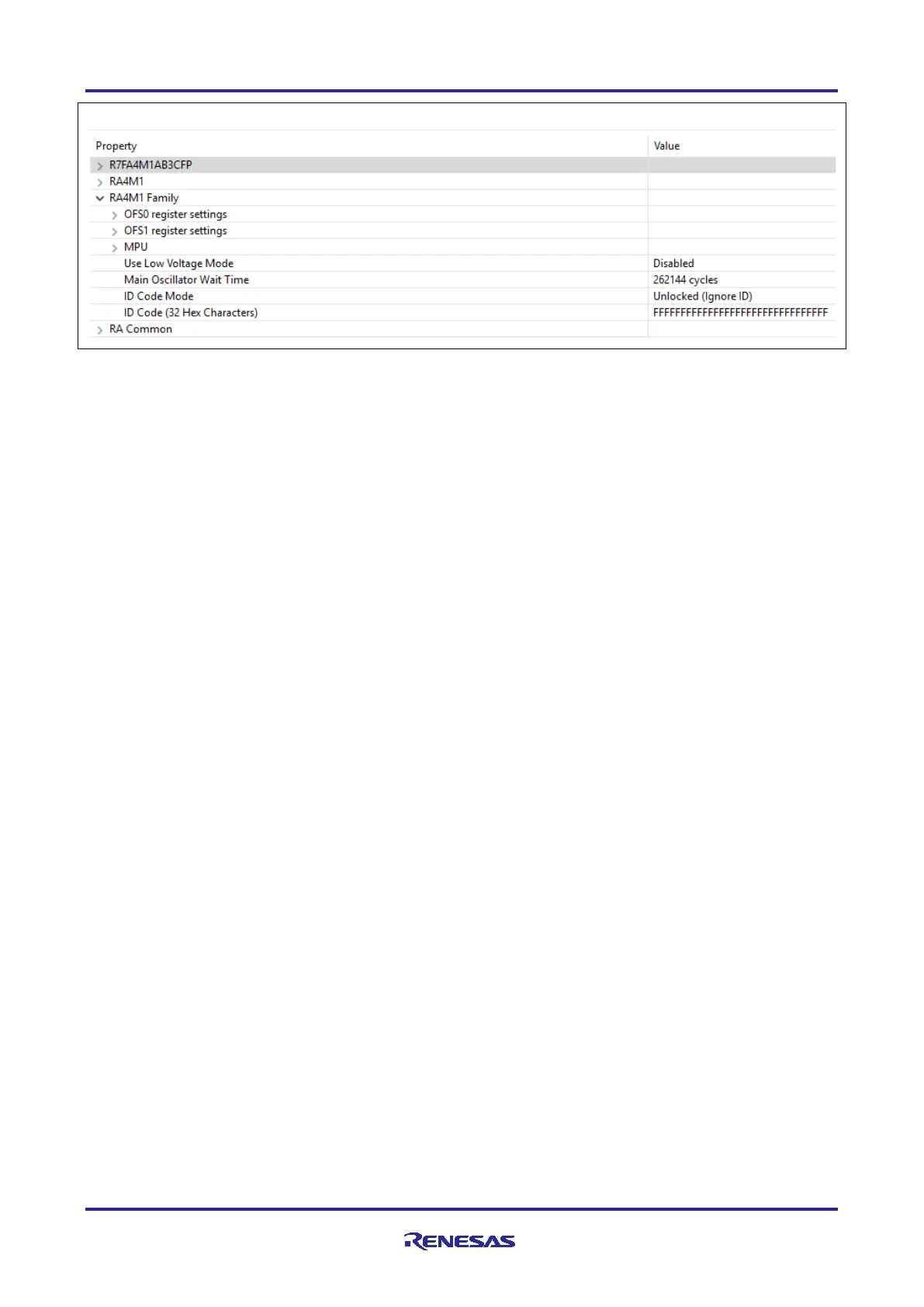

Figure 25. ID Code Setup for RA4M1 (Arm Cortex-M4 Core) Using Renesas FSP Configurator

Note: ID code protection settings must be handled carefully to prevent mistakes that may result in blocking

accesses to the MCU.

8.4.3 Flash Block Protection

RA4 MCUs with Arm Cortex-M33 core have a Flash Block Protection feature that protects secure or non-

secure flash region from being erased or reprogrammed by secure or non-secure software. It is worth noting

that the protection is for both Secure and Non-secure software accesses.

Refer to section “Configuring the Flash Block Protection” in Securing Data at Rest Using the Arm

®

TrustZone

®

application note for more details.

8.4.4 Memory Protection Unit

RA4 MCUs have a Memory Protection Unit (MPU). They have the ability to protect various MCU memory

regions from illegal access. The choices include allowing both reading and writing, prohibiting writing, and

prohibiting writing and reading. Select one of these options by setting the corresponding constant value at

the specific memory address. See ‘Memory Protection Unit’ in the MCU Hardware User’s Manual for more

details.

Loading...

Loading...