Renesas RA Family RA4 Quick Design Guide

R01AN5988EU0100 Rev.1.00 Page 30 of 51

Jul.21.21

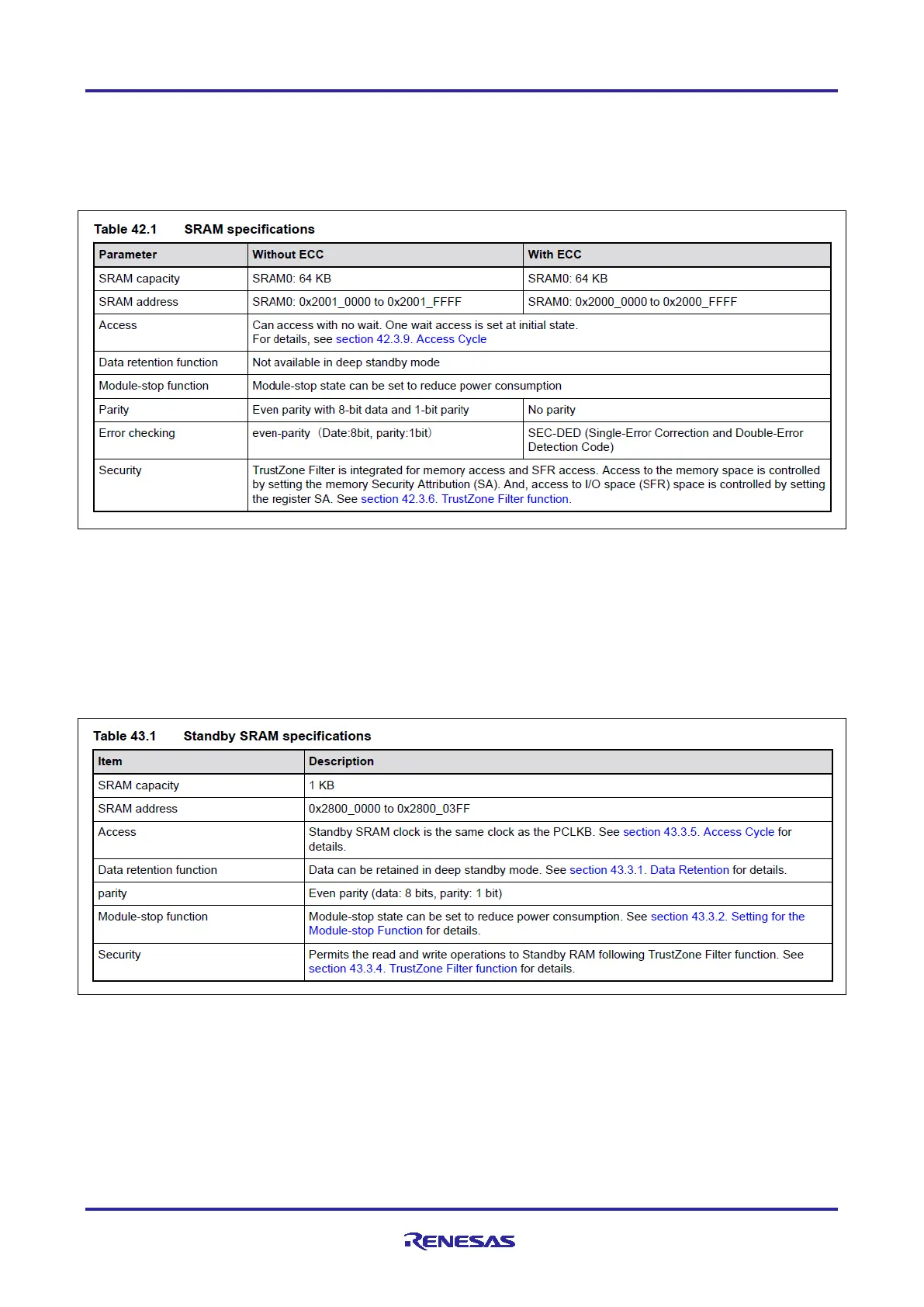

8.1 SRAM

The RA4 MCUs provide on-chip high-speed SRAM modules with either parity-bit checking or ECC (Error

Correction Code). The first 32 KB of SRAM0 is subject to ECC. Parity check is performed on other areas.

The following table lists the SRAM specifications. The number of SRAM modules and capacity vary by

device. Consult the Hardware User’s Manual for specifics.

Figure 21. RA4M3 SRAM Specification

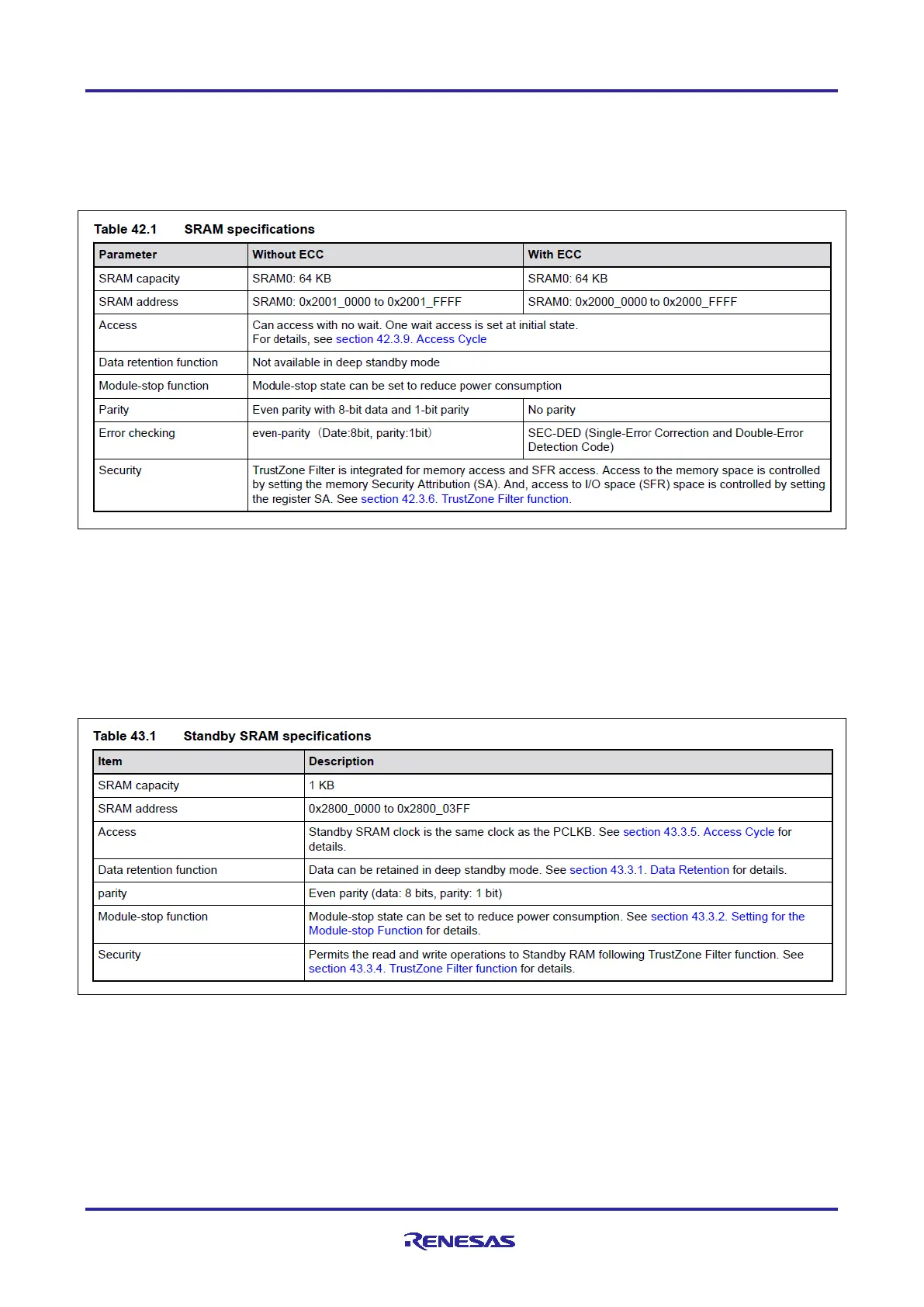

8.2 Standby SRAM

The RA4 MCUs provide an on-chip SRAM to retain data in Deep Software Standby mode. The table below

lists the Standby SRAM specifications.

The power supply to the Standby SRAM in Deep Software Standby mode is enabled by the

DPSBYCR.DEEPCUT[1:0] bits. If the DPSBYCR.DEEPCUT[1:0] bits are set to 00b, data in the Standby

SRAM is retained in Deep Software Standby mode. See section 11, Low Power Modes, for details on the

DPSBYCR.DEEPCUT[1:0] bits.

Figure 22. RA4M3 Standby SRAM Specification

The LPM (Low Power Mode) driver in Renesas FSP provides an option to cut or keep power to Standby

SRAM as shown in the following figure. The LPM driver’s APIs still need to be invoked to write the selected

settings to the MCU registers.

Loading...

Loading...