ChipScope Pro Software and Cores User Guide www.xilinx.com 27

UG029 (v14.3) October 16, 2012

ChipScope Pro Cores Description

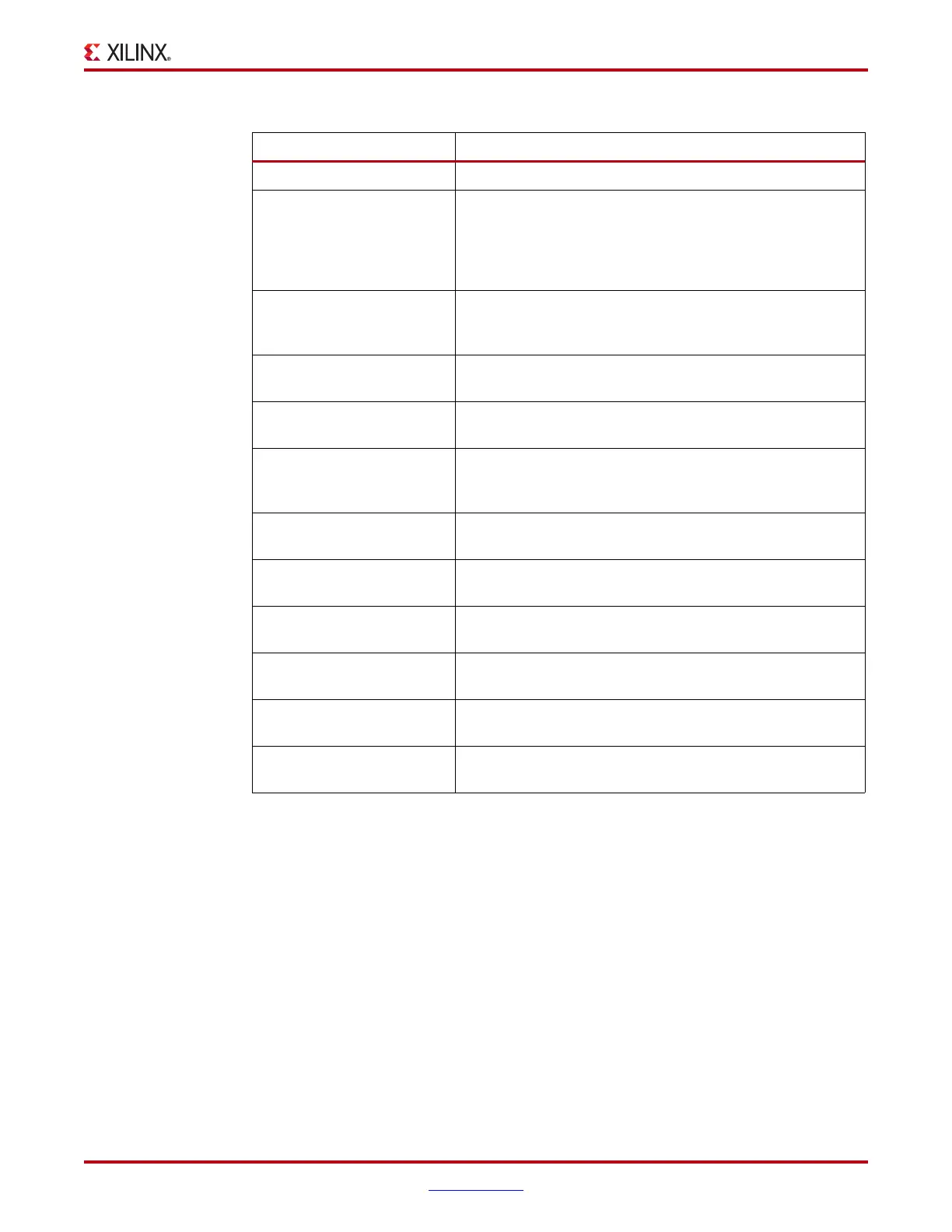

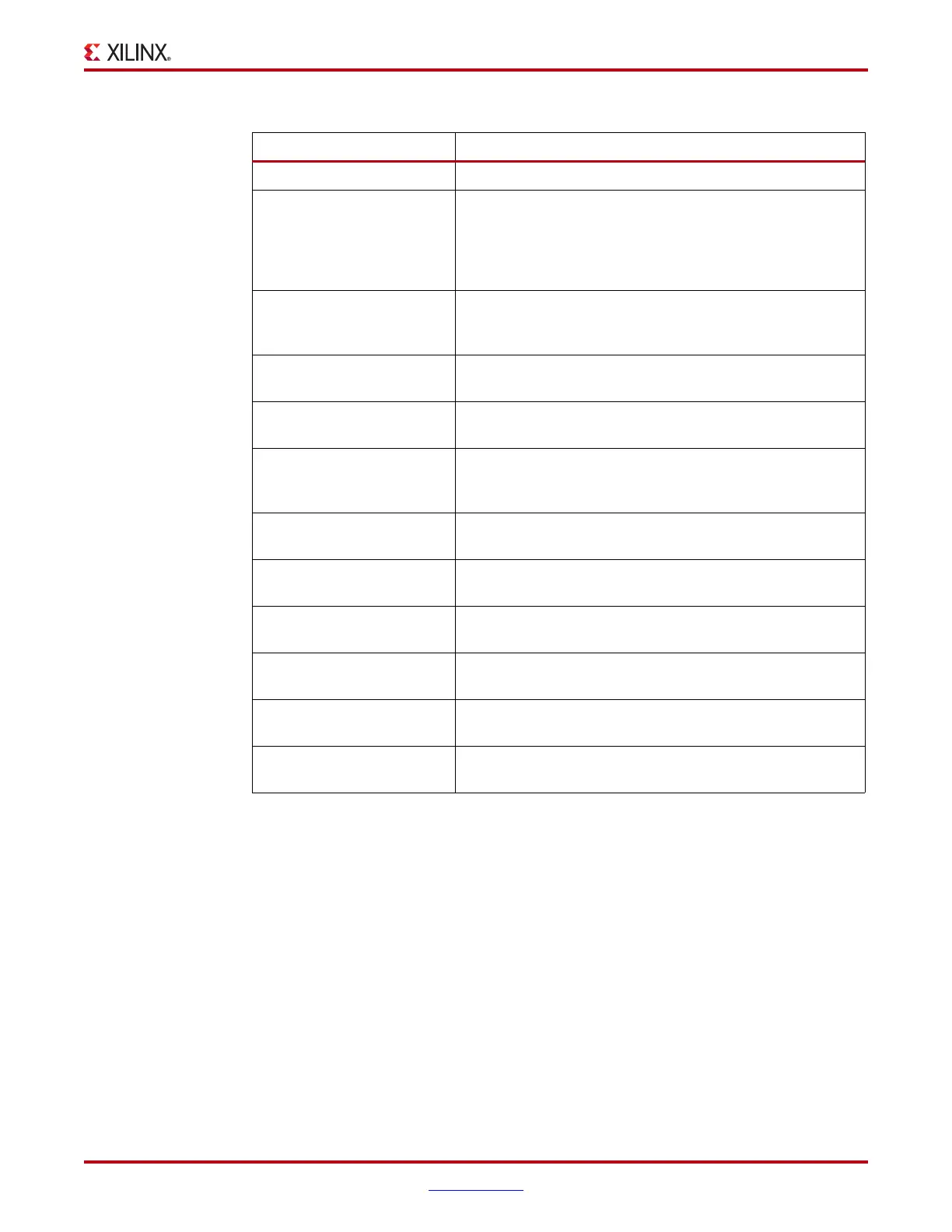

Table 1-11: IBERT v2.00a core for 7 Series FPGA GTZ Transceivers

Feature Description

Multiple GTZ Transceivers Up to eight transceivers can be selected per design.

Pattern Generator One pattern generator per selected GTZ transceiver is used.

PRBS 7-bit, PRBS 15-bit PRBS 23-bit, PRBS 31-bit, Clk 2x, and

Clk 10x patterns are available. The desired pattern from that

set can be selected individually for each GTZ transceiver at

runtime.

Pattern Checker One pattern checker per selected GTZ transceiver is used.

The same pattern set is available as the pattern generator. The

pattern can be chosen for each GTZ transceiver at runtime.

Fabric Width The FPGA fabric interface to the GTZ transceiver can only be

160 bits wide.

Polarity The polarity of the TX side of each GTZ transceiver can be

changed at runtime.

Reset Each GTZ transceiver can be reset independently. A reset is

also available to reset the entire MGT, including PLLs and

CPLLs.

Link and Lock Status Link, and CPLL/QPLL lock status are gathered for each GTZ

transceiver in the core.

DRP Read The contents of the DRP space for each GTZ transceiver can

be read independently of all others.

DRP Write The contents of the DRP for each GTZ transceiver can be

changed at runtime, with single-bit granularity.

Ports Read The contents of the registers that monitor the GTZ transceiver

ports can be read independently of others.

Ports Write The contents of the registers that control the GTZ

transceiver's ports can be changed at runtime.

Status The dynamic status information for the entire core can be

read out of the core at runtime.

Loading...

Loading...