Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 61

UG196 (v1.3) May 25, 2007

Shared PMA PLL

R

Table 5-2 defines the shared PMA PLL attributes.

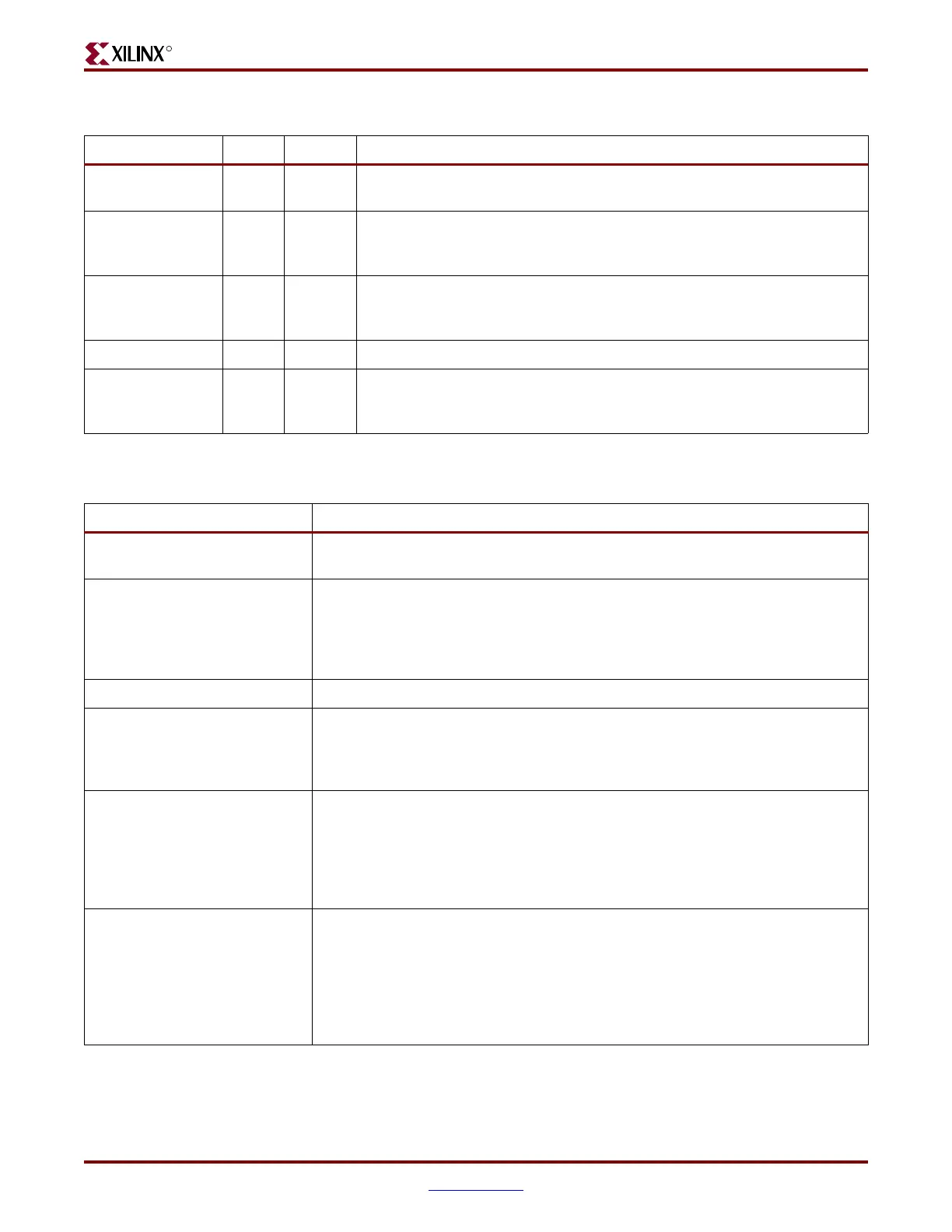

Table 5-1: Shared PMA PLL Ports

Port Dir Domain Description

CLKIN In Async

Reference clock input to the shared PMA PLL. See “Clocking,” page 68 for

more information about the different ways this port can be driven.

INTDATAWIDTH In Async

Sets the internal datapath width for the GTP_DUAL. If set to 0, the internal

datapath width is set to 8 bits. If set to 1, the internal datapath width is set to

10 bits.

PLLLKDET Out Async

This port indicates that the VCO rate is within acceptable tolerances of the

desired rate when High. Neither GTP transceiver in the tile operates reliably

until this condition is met.

PLLLKDETEN In Async This port enables the PLL lock detector and should always be tied High.

REFCLKOUT Out Async

The REFCLKOUT port from each GTP_DUAL tile provides direct access to

the reference clock provided to the shared PLL (CLKIN). It can be routed for

use in the FPGA logic.

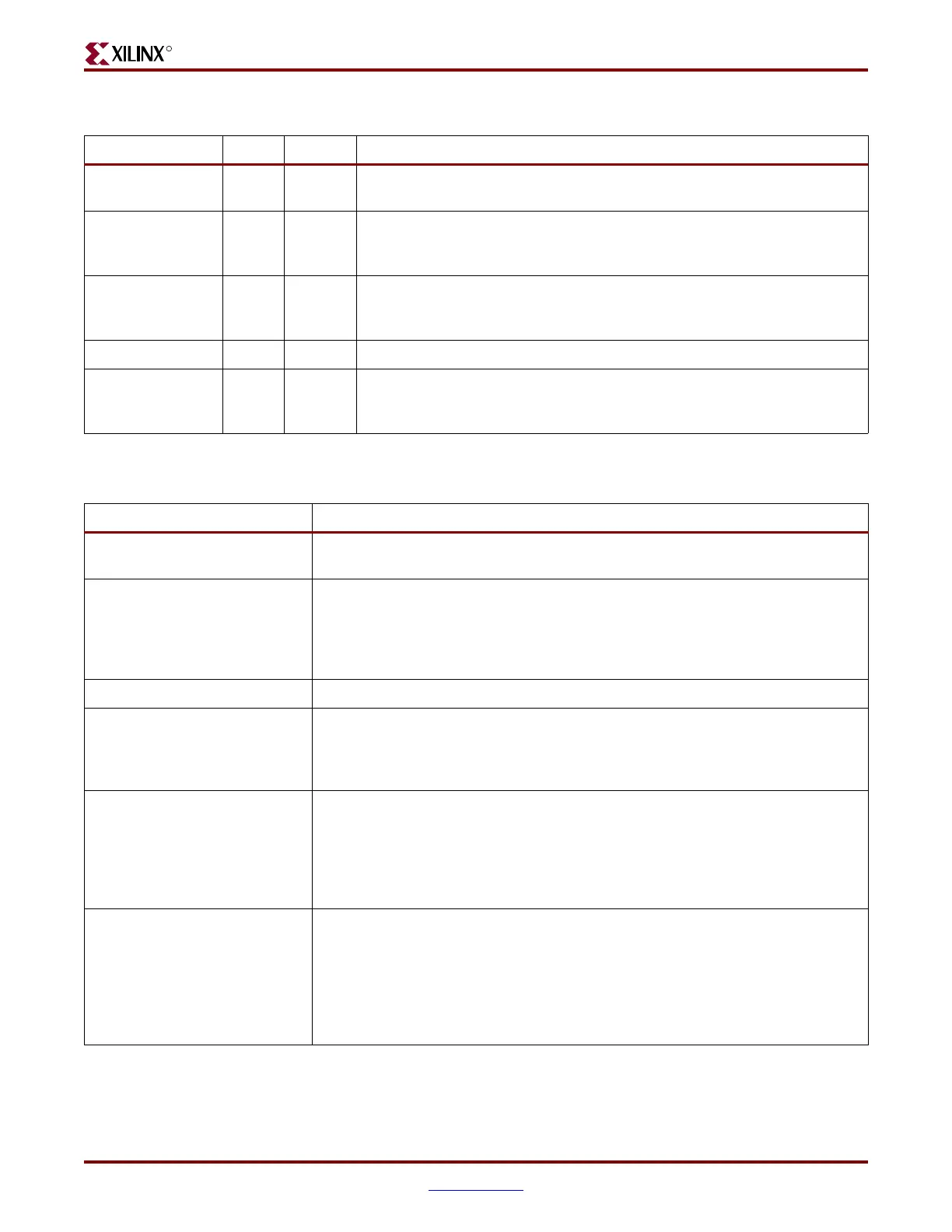

Table 5-2: Shared PMA PLL Attributes

Attribute Description

PCS_COM_CFG[27:0]

(1

For PLL_DIVSEL_FB = 1, set PCS_COM_CFG to 28’h1680A07, otherwise set to

28’h1680A0E (default).

PLL_DIVSEL_FB

Controls the feedback divider. Valid settings for PLL_DIVSEL_FB are 1, 2, 3, 4, and 5.

PLL_DIVSEL_FB is multiplied by 4 or 5, depending on the width of the internal

datapath as set by INTDATAWIDTH. If INTDATAWIDTH is Low, the feedback

divider N is set to PLL_DIVSEL_FB x 4. If INTDATAWIDTH is High, the feedback

divider N is set to PLL_DIVSEL_FB x 5.

PLL_DIVSEL_REF Controls the reference clock divider. Valid settings for PLL_DIVSEL_REF are 1 and 2.

PLL_RXDIVSEL_OUT_0

PLL_RXDIVSEL_OUT_1

Divides the PLL clock to produce a high-speed RX clock. Because both edges of the

clock are used, the divided clock must run at 1/2 the desired RX line rate. Permitted

divider settings are 1, 2, and 4. See “Serial In to Parallel Out (SIPO),” page 141 for

details.

PLL_TXDIVSEL_COMM_OUT

Divides the PLL clock to produce a high-speed TX clock. Because both edges of the

clock are used, the divided clock must run at 1/2 the desired TX line rate. Permitted

divider settings are 1, 2, and 4. This divider provides a clock to both GTP transceivers

and should be used when the same divider value is needed for both. When

PLL_TXDIVSEL_COMM_OUT is used, both PLL_TXDIVSEL_OUT attributes must

be set to 1. See “Parallel In to Serial Out (PISO),” page 110 for details.

PLL_TXDIVSEL_OUT_0

PLL_TXDIVSEL_OUT_1

Divides the PLL clock to produce a high-speed TX clock. Because both edges of the

clock are used, the divided clock must run at 1/2 the desired TX line rate. Permitted

divider settings are 1, 2, and 4. Each GTP transceiver has its own

PLL_TXDIVSEL_OUT. If the transceivers require different dividers, these attributes

must be used instead of PLL_TXDIVSEL_COMM_OUT, and

PLL_TXDIVSEL_COMM_OUT must be set to 1. See “Parallel In to Serial Out

(PISO),” page 110 for details.

Notes:

1. In ISE 9.2i and above, this attribute is included in the GTP_DUAL instance. Older ISE versions require setting this attribute with the

a user-constraints file (UCF) when a non-default value is needed.

Loading...

Loading...