ZCU111 Board User Guide 54

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Chapter 3: Board Component Descriptions

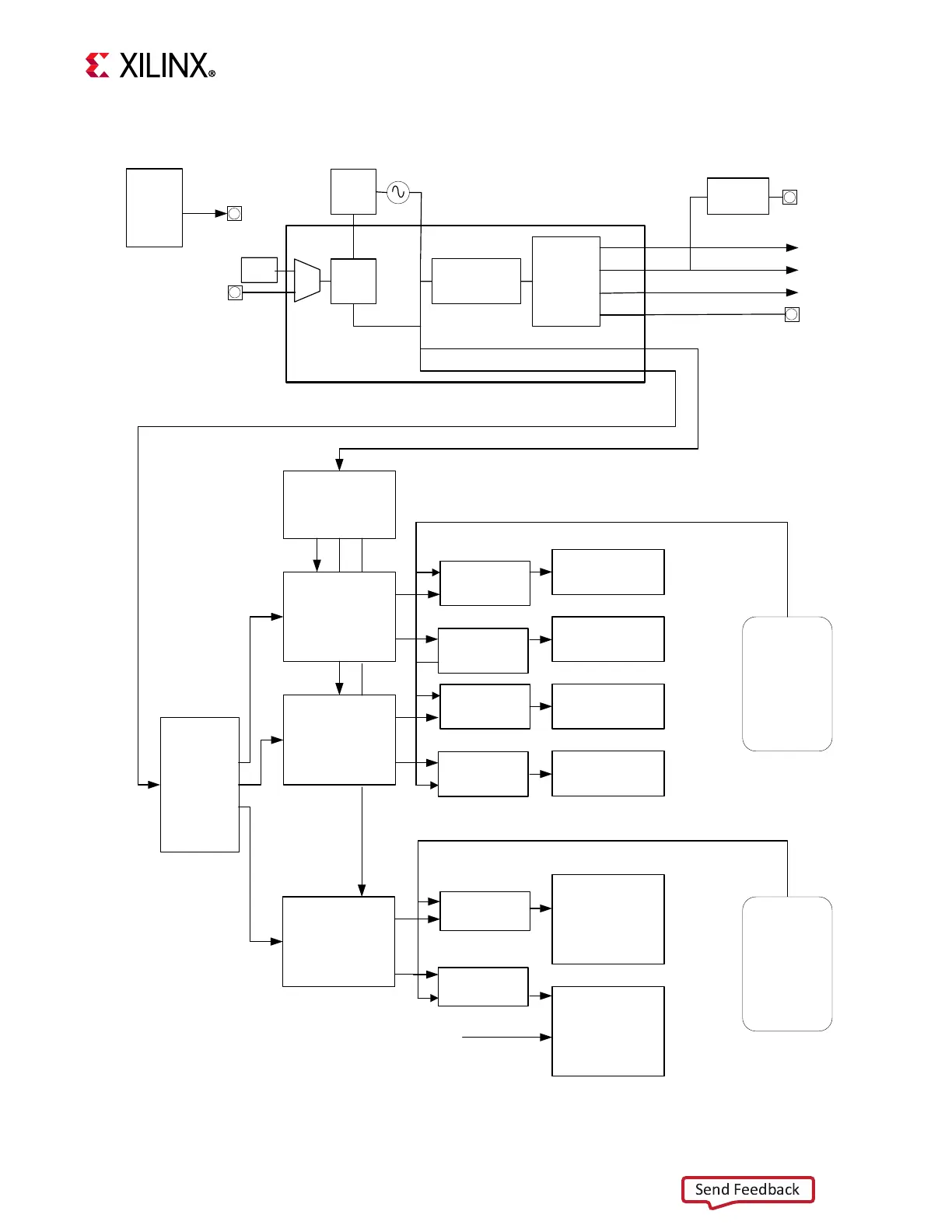

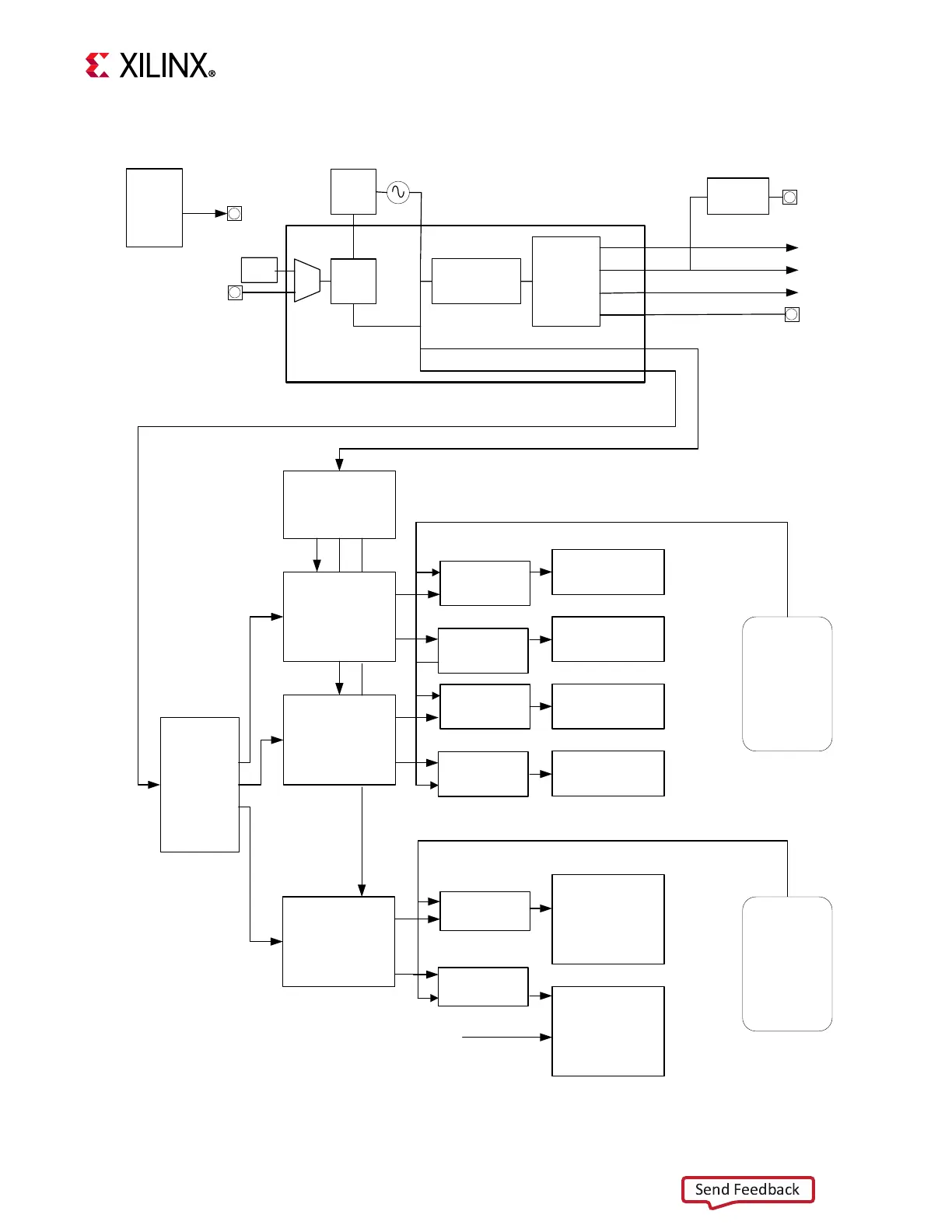

Figure 3-18 shows the bank view of the ZCU111 RF clocking structure.

X-Ref Target - Figure 3-18

Figure 3-18: RF Clocking Structure for ADC and DAC Banks

ADC Bank 225

2 ADC, 1 CLKIN

ADC Bank 224

2 ADC, 1 CLKIN

DAC Bank 228

4 DAC, 1 CLKIN

LMX2594

RF1 PLL

PLL1

PLL2

(incl. VCO)

Dividers

CLKout0

Loop

Filter

VCXO

122.88 MHz

CLKout3

CLKout4

CLKout2

CLKout5

CLKout1

TCXO

LMK04208

OSCinCPout1

CLKin0

CLKin1

SMA External REF

Clock

Buffer

LMK00304

MPSoC DAC: SYSREF_RFSOC

MPSoC PL: FPGA_REFCLK_OUT

ADC

Connector

Samtec

LPAF

8x40

RF outA

MPSoC PL: SYSREF_FPGA

RF outB

Capacitor Option

ADC Bank 227

2 ADC, 1 CLKIN

ADC Bank 226

2 ADC, 1 CLKIN

LMX2594

RF2 PLL

RF outA

RF outB

LMX2594

RF3 PLL

RF outA

RF outB

DAC Bank 229

4 DAC, 1 CLKIN

Capacitor Option

SYSREF_RFSoC

/2

/2

/1

/2

/2

/2

RF1_CLK0_A

RF1_CLK0_B

RF2_CLK0_B

RF2_CLK0_A

RF3_CLK0_A

RF3_CLK0_B

/2

/2

SMA: ~10 MHz REF Out

/2

Sync

Buffer

LMK00804

FPGA

Bank

64

SMA: AMS_FPGA_REF_CLK

REFIN_2594

SYNC

/1

/2

/2

/2

Capacitor Option

/8 (4 pairs)

Capacitor Option

Capacitor Option

ADCLK_IN0-3

DAC

Connector

Samtec

LPAF

8x40

Capacitor Option

DACLK_IN0-1

/4 (2 pairs)

Capacitor

Option

Optional DAC:

SYSREF_RFSOC

ADC0

ADC1

ADC2

ADC3

DAC0

DAC1

X21144-062818

Loading...

Loading...