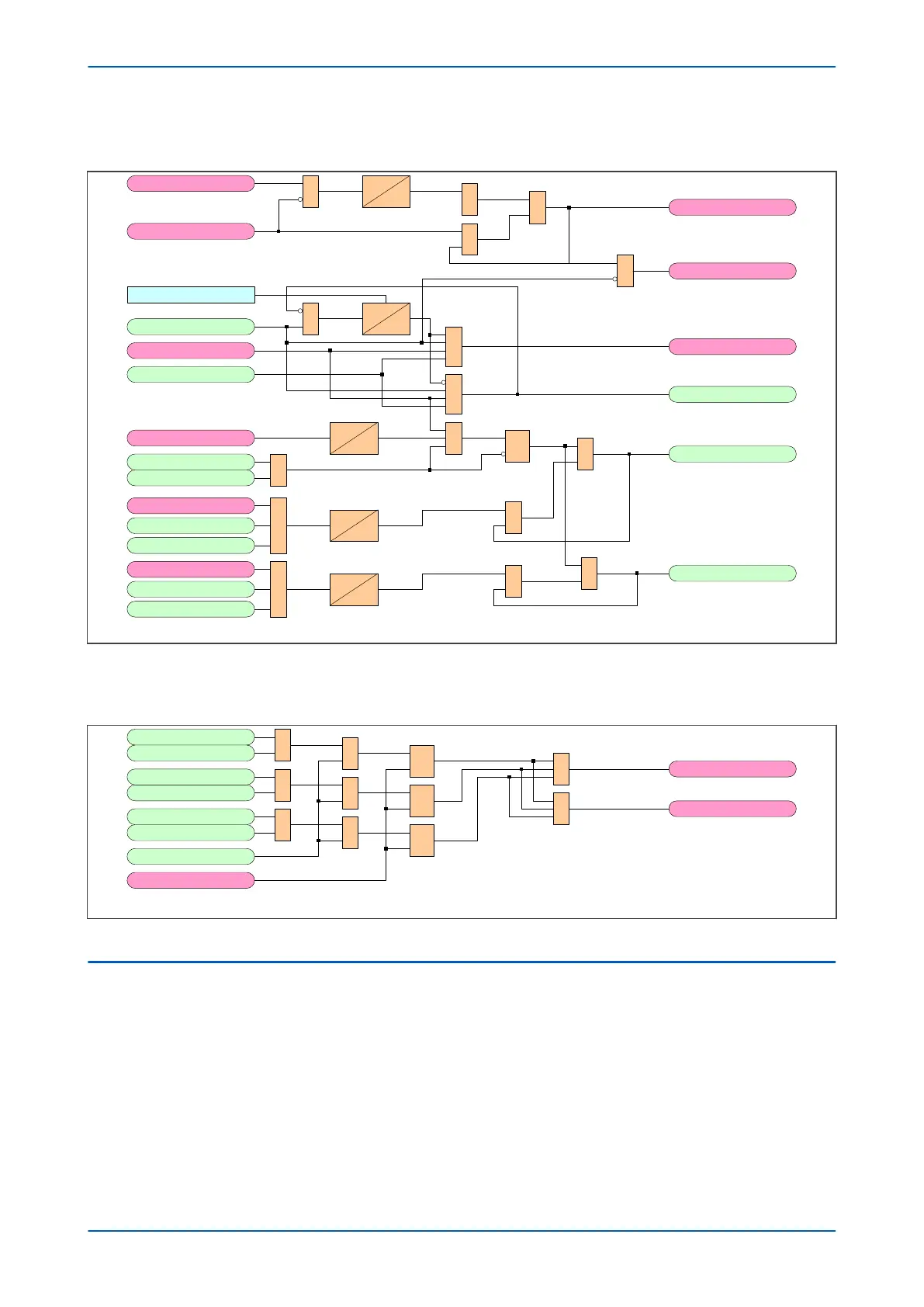

5.8.5 PROTECTION REOPERATION AND EVOLVING FAULT LOGIC DIAGRAM

V03332

TARANY

&

TMEMANY

Prot ReOp

LastShot

Set CB1 CL

1P DTime

Seq Counter = 1

CB1 AR Lockout

CB1 Closed 3 ph

CB1 ARIP

Prot ReOp

Evolve Lock

Evolve 3Ph

CB1 Failed AR

&

&

1

0

0.02

&

Discrim Time

t

0

&

&

0

0.02

R

Q

S

&

&

10

0.02

&

&

RESETL-F

Set CB2 CL

CB2 Closed 3 ph

CB2 ARIP

10

0.02

&

& CB2 Failed AR

CB2 AR Lockout

1

1554

847

306

328

907

1544

915

1544

576

1550

1441

Figure 161: Protection Reoperation and Evolving Fault logic diagram (Module 20)

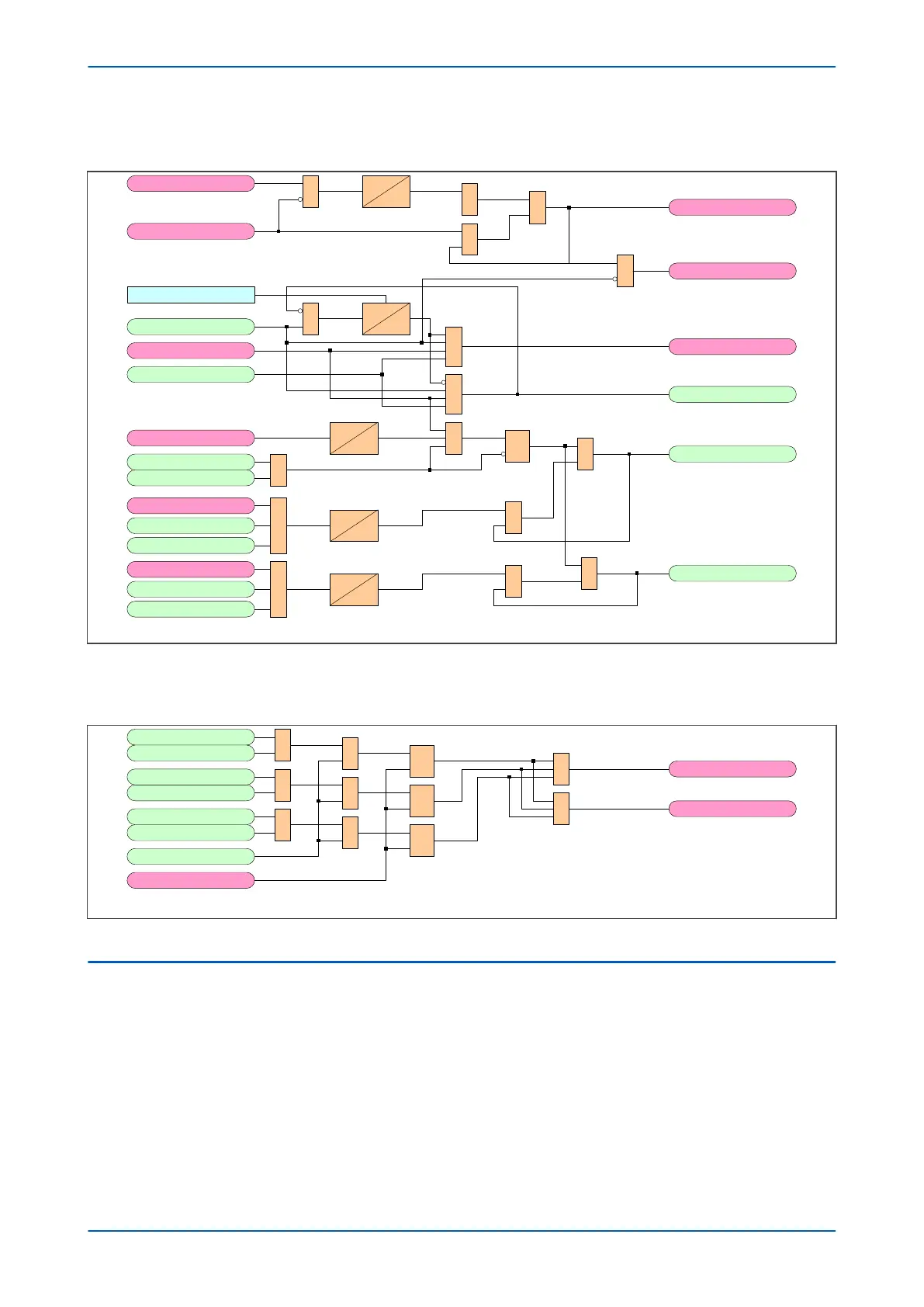

5.8.6

FAULT MEMORY LOGIC DIAGRAM

V03320

RESPRMEM

Trip Inputs A

Ext Fault APh

FLTMEM 2P

&

FLTMEM 3P

AR Start

Trip Inputs B

Trip Inputs C

Ext Fault BPh

Ext Fault CPh

1

1

1

&

&

R

Q

S

R

Q

S

R

Q

S

=

2

&

Figure 162: Fault Memory logic diagram (Module 15)

5.9

AUTORECLOSE IN PROGRESS

The AR In Progress module produces various signals to indicate to other modules and functions that an

Autoreclose operation is currently in progress.

Chapter 11 - Autoreclose P446SV

302 P446SV-TM-EN-1

Loading...

Loading...