LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

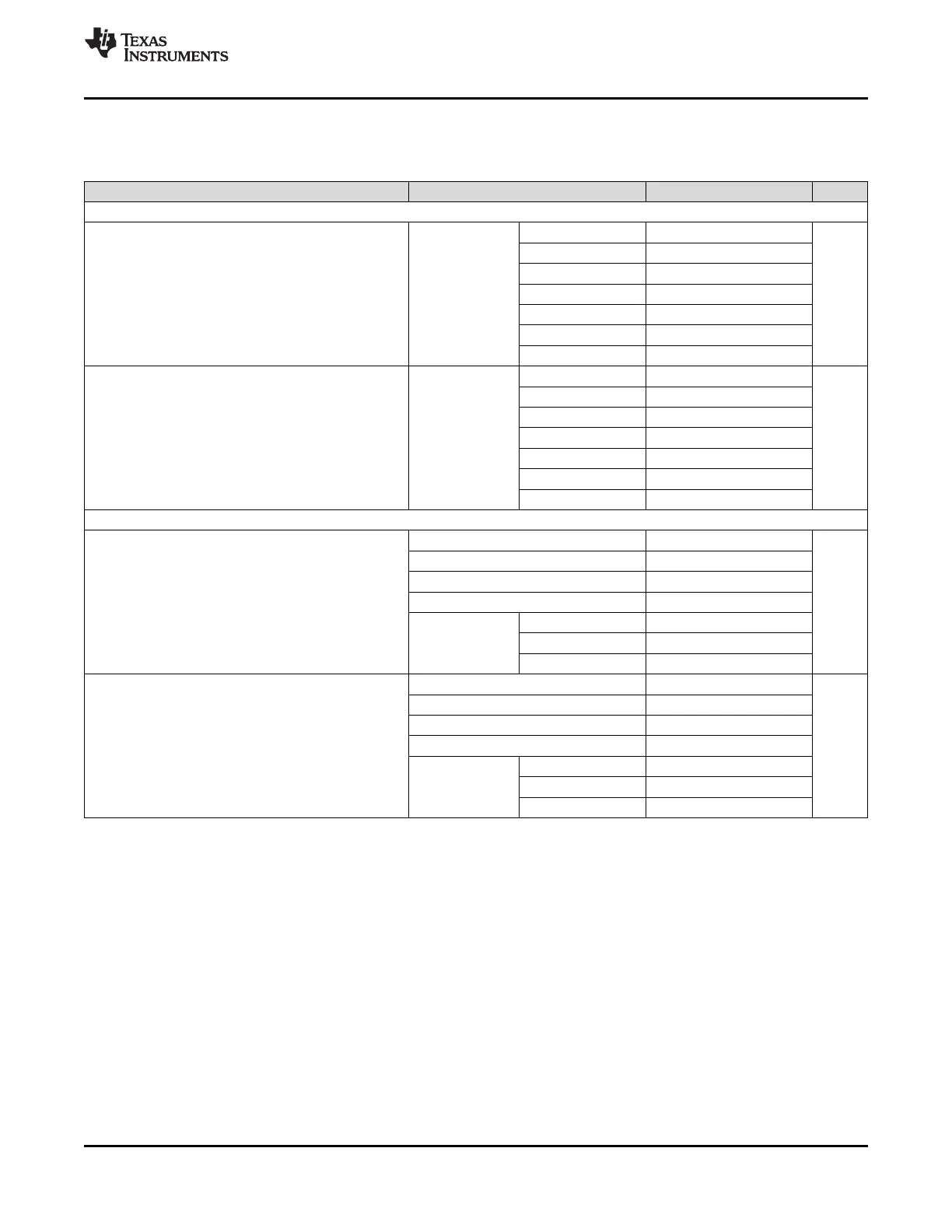

Electrical Characteristics (continued)

(3.15 V < V

CC

< 3.45 V, –40 °C < T

A

< 85 °C and T

PCB

≤ 105 °C. Typical values at V

CC

= 3.3 V, T

A

= 25 °C, at the

Recommended Operating Conditions and are not assured.)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

NOISE FLOOR (continued)

LVDS –156.3

HSDS 6 mA –158.4

HSDS 8 mA –159.3

LMK04828, VCO0, Noise Floor

L(f)

CLKout

245.76 MHz HSDS 10 mA –158.9 dBc/Hz

20 MHz Offset

(15)

LVPECL16 /w 240 Ω –161.6

LVPECL20 /w 240 Ω –162.5

LCPECL –162.1

LVDS –155.7

HSDS 6 mA –157.5

HSDS 8 mA –158.1

LMK04828, VCO1, Noise Floor

L(f)

CLKout

245.76 MHz HSDS 10 mA –157.7 dBc/Hz

20 MHz Offset

(15)

LVPECL16 /w 240 Ω –160.3

LVPECL20 /w 240 Ω –161.1

LCPECL –160.8

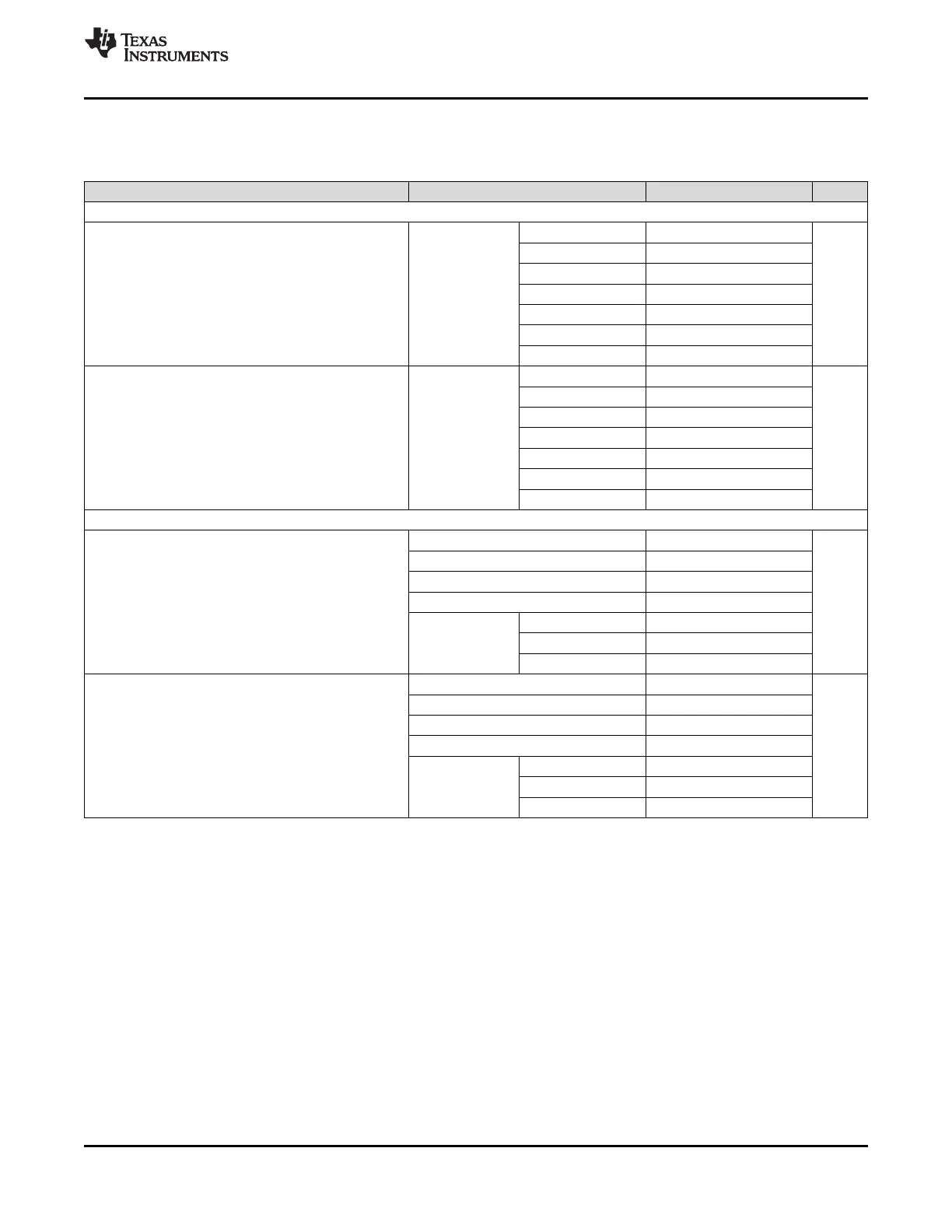

CLKout CLOSED LOOP PHASE NOISE SPECIFICATIONS a COMMERCIAL QUALITY VCXO

(16)

Offset = 1 kHz –126.9

Offset = 10 kHz –133.5

LMK04821

Offset = 100 kHz –135.4

VCO0

L(f)

CLKout

Offset = 1 MHz –149.8 dBc/Hz

SSB Phase Noise

(13)

LVDS –158.1

245.76 MHz

Offset = 10 MHz HSDS 8 mA –161.1

LVPECL16 /w 240 Ω –161.7

Offset = 1 kHz –126.8

Offset = 10 kHz –133.4

LMK04821

Offset = 100 kHz –135.4

VCO1

L(f)

CLKout

Offset = 1 MHz –151.8 dBc/Hz

SSB Phase Noise

(13)

LVDS –157.2

245.76 MHz

Offset = 10 MHz HSDS 8 mA –159.1

LVPECL16 /w 240 Ω –158.9

(15) Data collected using ADT2-1T+ balun. Loop filter is C1 = 47 pF, C2 = 3.9 nF, R2 = 620 Ω, C3 = 10 pF, R3 = 200 Ω, C4 = 10 pF, R4 =

200 Ω, PLL1_CP = 450 µA, PLL2_CP = 3.2 mA.. VCO0 loop filter bandwidth = 344 kHz, phase margin = 73 degrees. VCO1 Loop filter

loop bandwidth = 233 kHz, phase margin = 70 degrees. CLKoutX_Y_IDL = 1, CLKoutX_Y_ODL = 0.

(16) VCXO used is a 122.88 MHz Crystek CVHD-950-122.880.

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 15

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...