LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

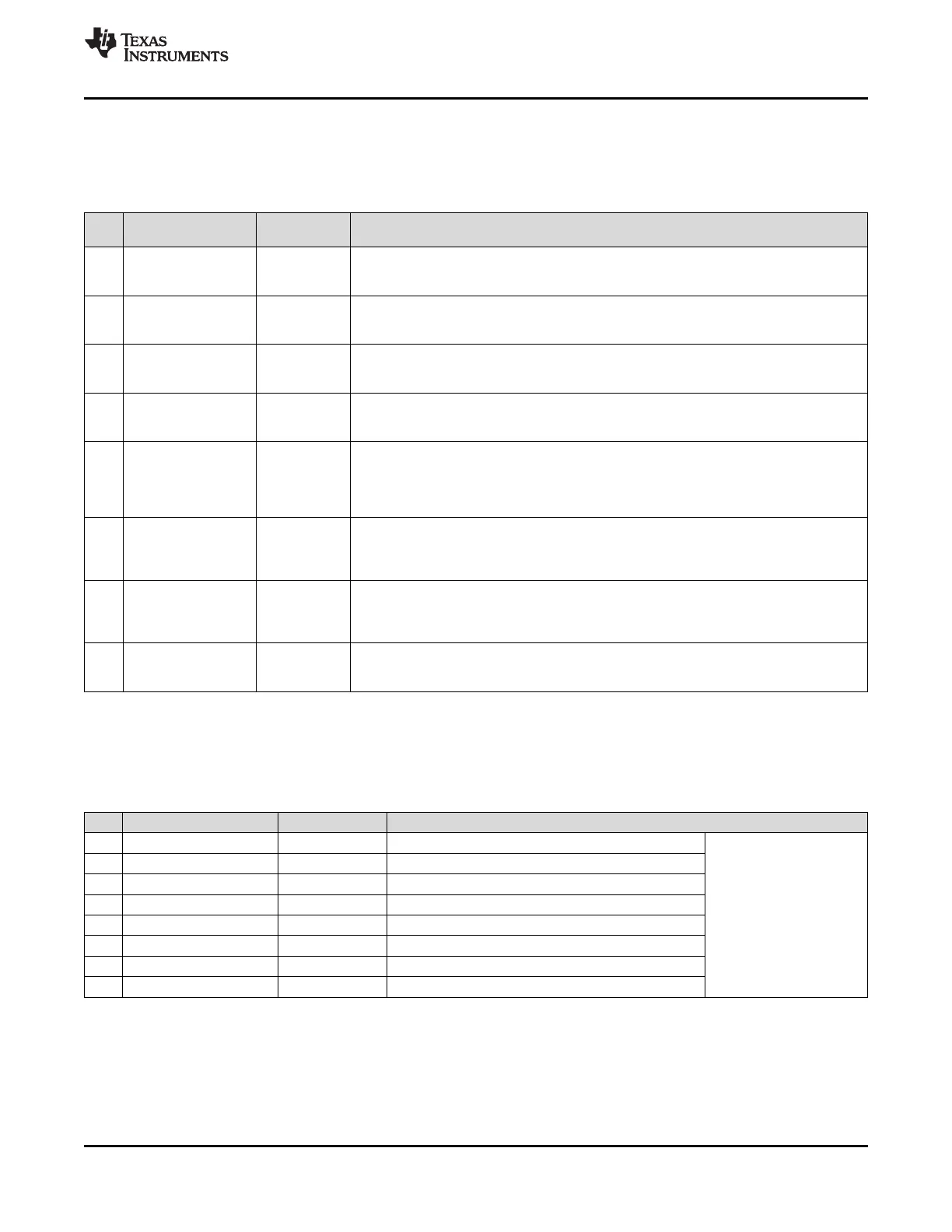

9.7.3.7 PLL1_PD, VCO_LDO_PD, VCO_PD, OSCin_PD, SYSREF_GBL_PD, SYSREF_PD,

SYSREF_DDLY_PD, SYSREF_PLSR_PD

This register contains powerdown controls for OSCin and SYSREF functions.

Table 29. Register 0x140

POR

BIT NAME DESCRIPTION

DEFAULT

Powerdown PLL1

7 PLL1_PD 0 0: Normal operation

1: Powerdown

Powerdown VCO_LDO

6 VCO_LDO_PD 0 0: Normal operation

1: Powerdown

Powerdown VCO

5 VCO_PD 0 0: Normal operation

1: Powerdown

Powerdown the OSCin port.

4 OSCin_PD 0 0: Normal operation

1: Powerdown

Powerdown individual SYSREF outputs depending on the setting of

SDCLKoutY_DIS_MODE for each SYSREF output. SYSREF_GBL_PD allows many

3 SYSREF_GBL_PD 0 SYSREF outputs to be controlled through a single bit.

0: Normal operation

1: Activate Powerdown Mode

Powerdown the SYSREF circuitry and divider. If powered down, SYSREF output mode

cannot be used. SYNC cannot be provided either.

2 SYSREF_PD 1

0: SYSREF can be used as programmed by individual SYSREF output registers.

1: Powerdown

Powerdown the SYSREF digital delay circuitry.

0: Normal operation, SYSREF digital delay may be used. Must be powered up during

1 SYSREF_DDLY_PD 1

SYNC for deterministic phase relationship with other clocks.

1: Powerdown

Powerdown the SYSREF pulse generator.

0 SYSREF_PLSR_PD 1 0: Normal operation

1: Powerdown

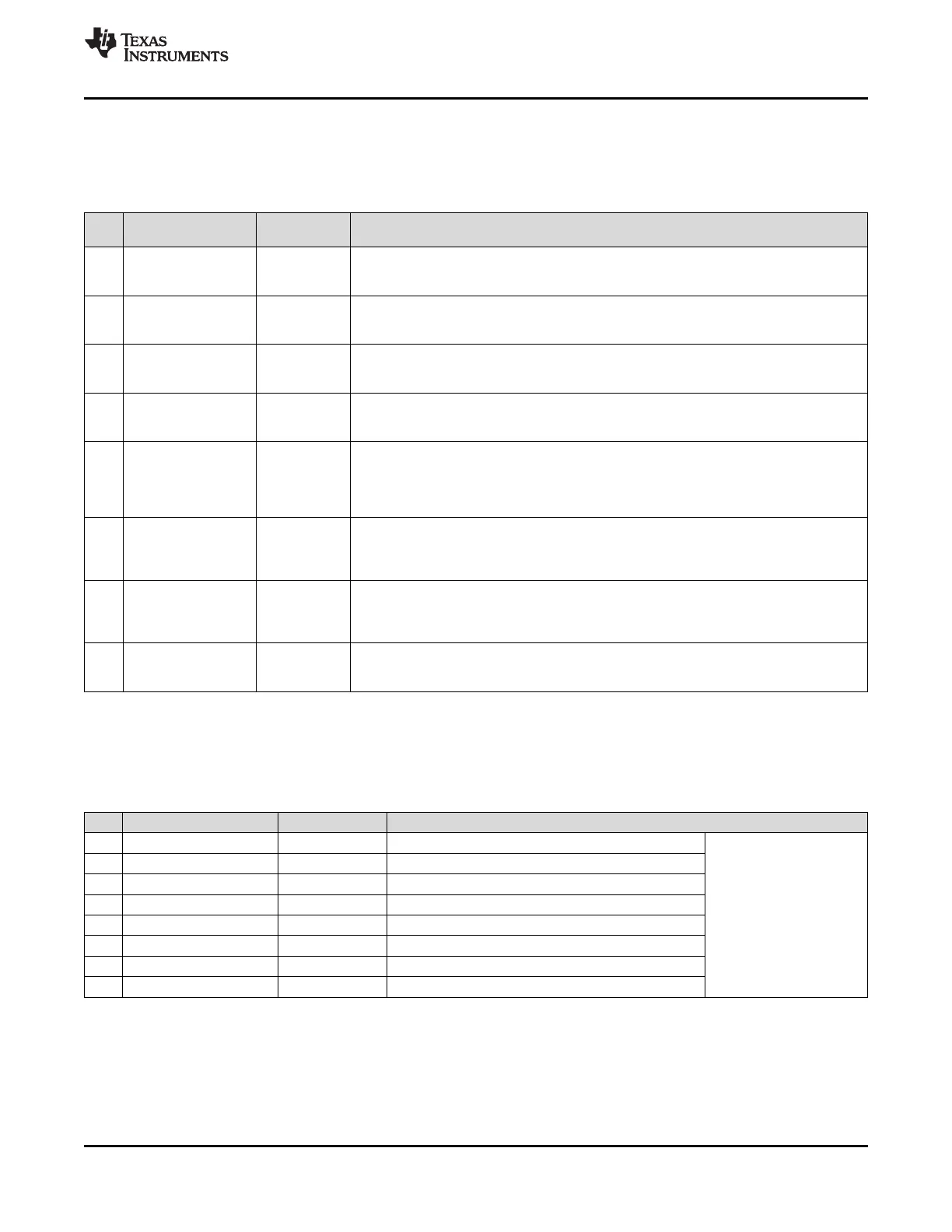

9.7.3.8 DDLYdSYSREF_EN, DDLYdX_EN

This register enables dynamic digital delay for enabled device clocks and SYSREF when DDLYd_STEP_CNT is

programmed.

Table 30. Register 0x141

BIT NAME POR DEFAULT DESCRIPTION

7 DDLYd _SYSREF_EN 0 Enables dynamic digital delay on SYSREF outputs

6 DDLYd12_EN 0 Enables dynamic digital delay on DCLKout12

5 DDLYd10_EN 0 Enables dynamic digital delay on DCLKout10

4 DDLYd8_EN 0 Enables dynamic digital delay on DCLKout8

0: Disabled

1: Enabled

3 DDLYd6_EN 0 Enables dynamic digital delay on DCLKout6

2 DDLYd4_EN 0 Enables dynamic digital delay on DCLKout4

1 DDLYd2_EN 0 Enables dynamic digital delay on DCLKout2

0 DDLYd0_EN 0 Enables dynamic digital delay on DCLKout0

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 65

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...