LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

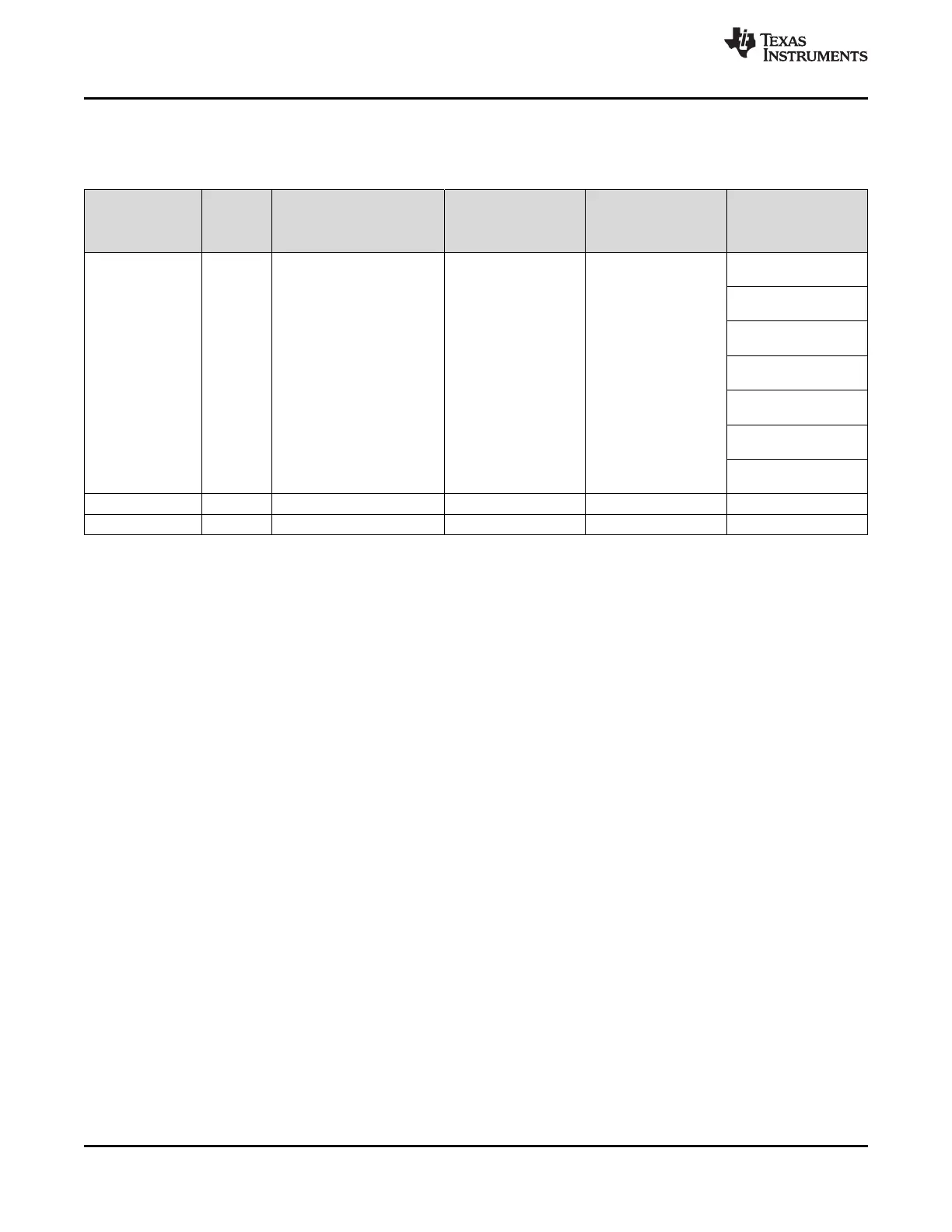

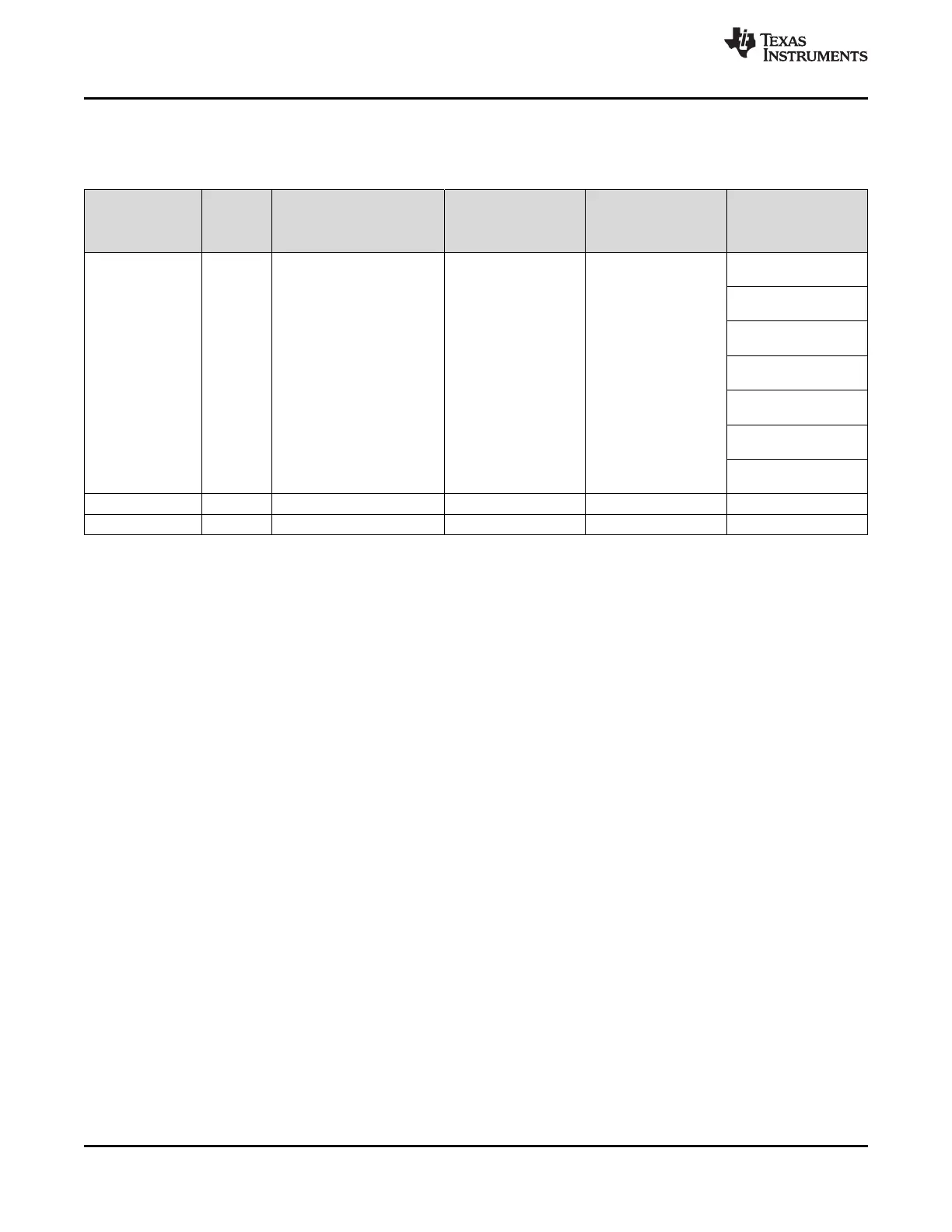

5 Device Comparison Table

5.1 Device Configuration Information

PLL2

REF-

OSCout (BUFFERED

PROGRAMMABLE

ERENCE

PART NUMBER OSCin Clock) LVDS/ VCO0 FREQUENCY VCO1 FREQUENCY

LVDS/LVPECL/HSDS

LVPECL/ LVCMOS

(1)

INPUTS

(1)

OUTPUTS

VCO1_DIV = ÷2

1460 to 1540 MHz

VCO1_DIV = ÷3

974 to 1026 MHz

VCO1_DIV = ÷4

730 to 770 MHz

VCO1_DIV = ÷5

LMK04821 Up to 3 Up to 1 14 1930 to 2075 MHz

584 to 616 MHz

VCO1_DIV = ÷6

487 to 513 MHz

VCO1_DIV = ÷7

418 to 440 MHz

VCO1_DIV = ÷8

365 to 385 MHz

LMK04826B Up to 3 Up to 1 14 1840 to 1970 MHz 2440 to 2505 MHz

LMK04828B Up to 3 Up to 1 14 2370 to 2630 MHz 2920 to 3080 MHz

(1) OSCout may also be third clock input, CLKin2.

6 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...