LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

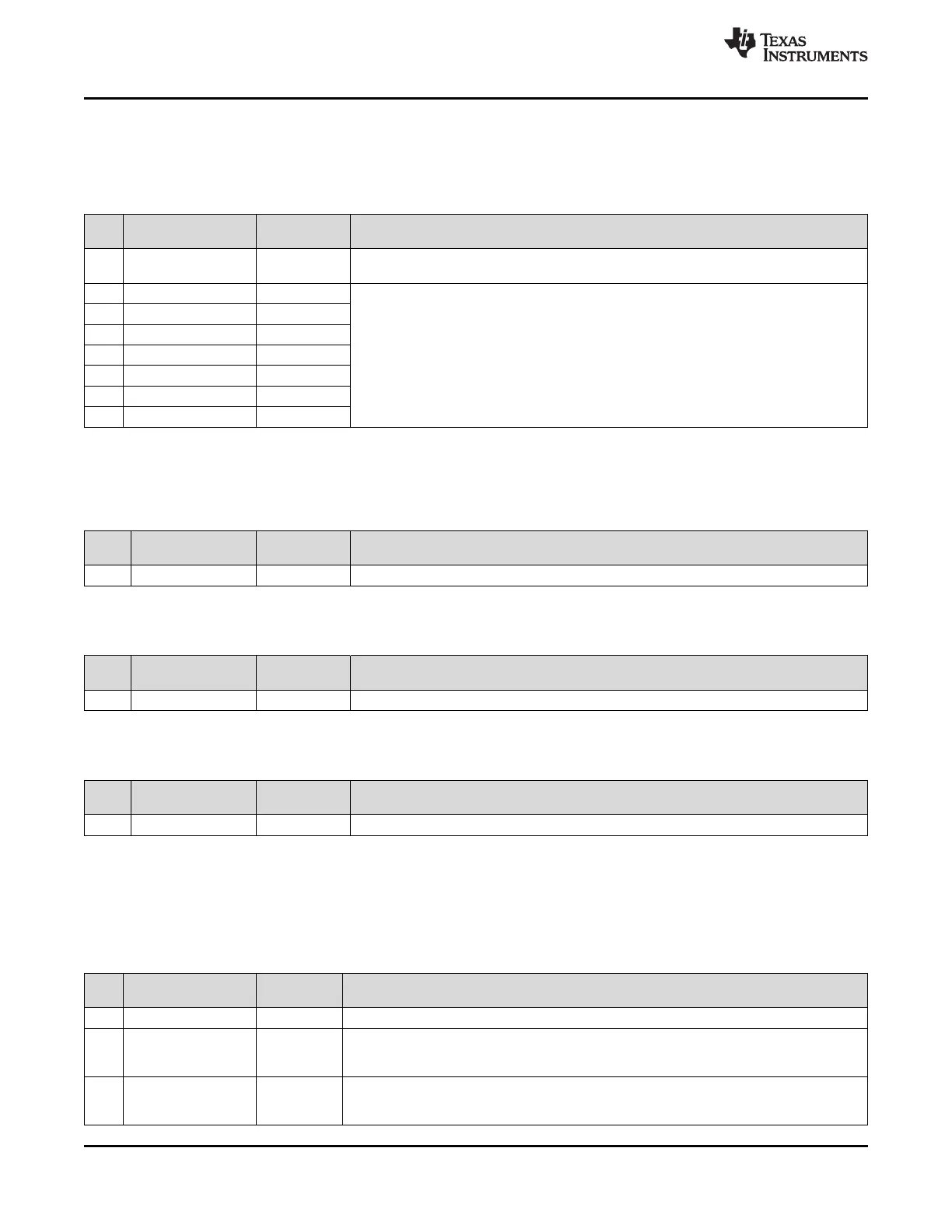

9.7.3.11 SYNC_DISSYSREF, SYNC_DISX

SYNC_DISX will prevent a clock output from being synchronized or interrupted by a SYNC event or when

outputting SYSREF.

Table 33. Register 0x144

POR

BIT NAME DESCRIPTION

DEFAULT

Prevent the SYSREF clocks from becoming synchronized during a SYNC event. If

7 SYNC_DISSYSREF 0

SYNC_DISSYSREF is enabled it will continue to operate normally during a SYNC event.

6 SYNC_DIS12 0

5 SYNC_DIS10 0

4 SYNC_DIS8 0

Prevent the device clock output from becoming synchronized during a SYNC event or

3 SYNC_DIS6 0 SYSREF clock. If SYNC_DIS bit for a particular output is enabled then it will continue to

operate normally during a SYNC event or SYSREF clock.

2 SYNC_DIS4 0

1 SYNC_DIS2 0

0 SYNC_DIS0 0

9.7.3.12 Fixed Register

Always program this register to value 127.

Table 34. Register 0x145

POR

BIT NAME DESCRIPTION

DEFAULT

7:0 Fixed Register 0 Always program to 127

Always program this register to value 170.

Table 35. Register 0x171

POR

BIT NAME DESCRIPTION

DEFAULT

7:0 Fixed Register 10 (0x0A) Always program to 170 (0xAA)

Always program this register to value 2.

Table 36. Register 0x172

POR

BIT NAME DESCRIPTION

DEFAULT

7:0 Fixed Register 0 Always program to 2 (0x02)

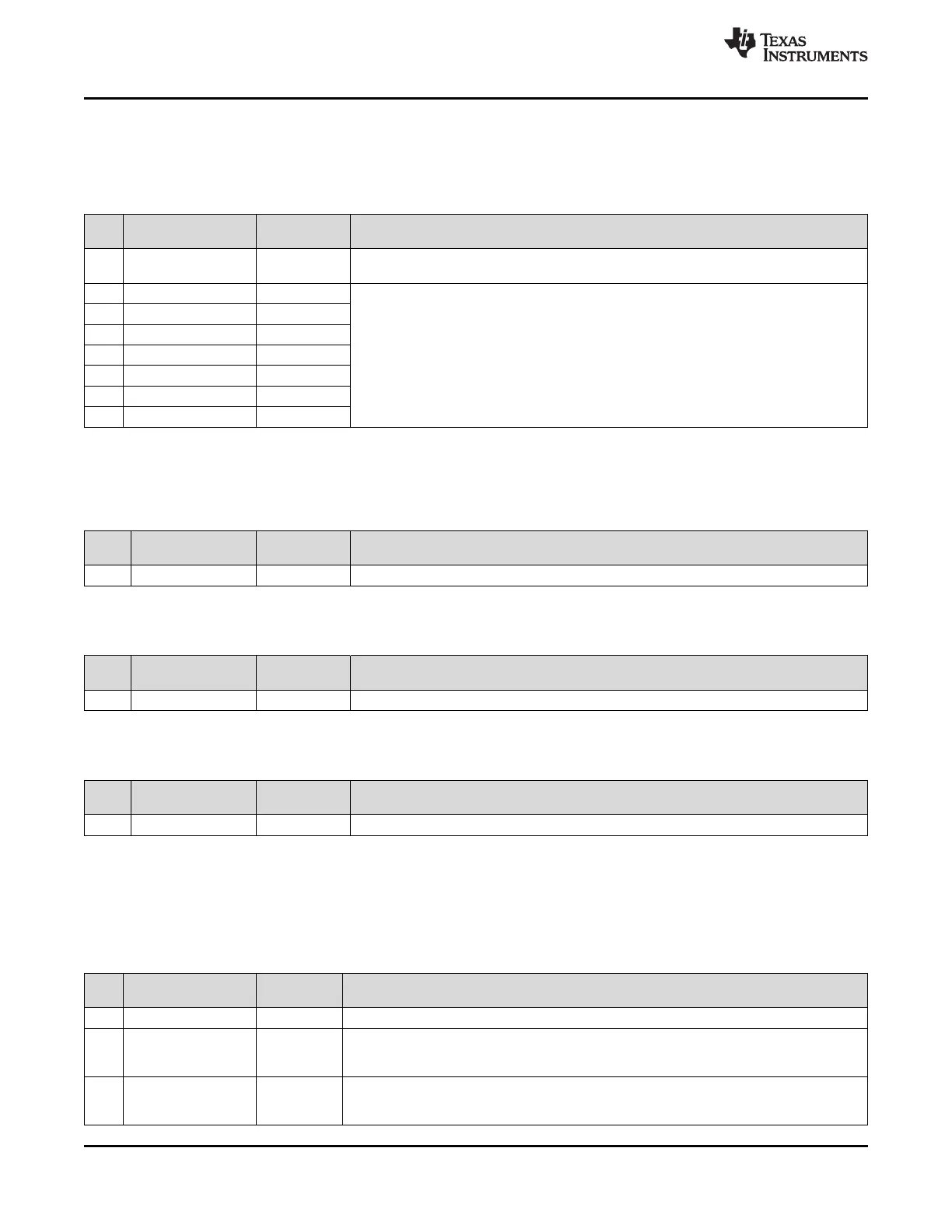

9.7.4 (0x146 - 0x149) CLKin Control

9.7.4.1 CLKin2_EN, CLKin1_EN, CLKin0_EN, CLKin2_TYPE, CLKin1_TYPE, CLKin0_TYPE

This register has CLKin enable and type controls.

Table 37. Register 0x146

BIT POR

NAME DESCRIPTION

DEFAULT

7:6 NA 0 Reserved

Enable CLKin2 to be used during auto-switching of CLKin_SEL_MODE.

5 CLKin2_EN 0 0: Not enabled for auto mode

1: Enabled for auto mode

Enable CLKin1 to be used during auto-switching of CLKin_SEL_MODE.

4 CLKin1_EN 1 0: Not enabled for auto mode

1: Enabled for auto mode

68 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...