LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

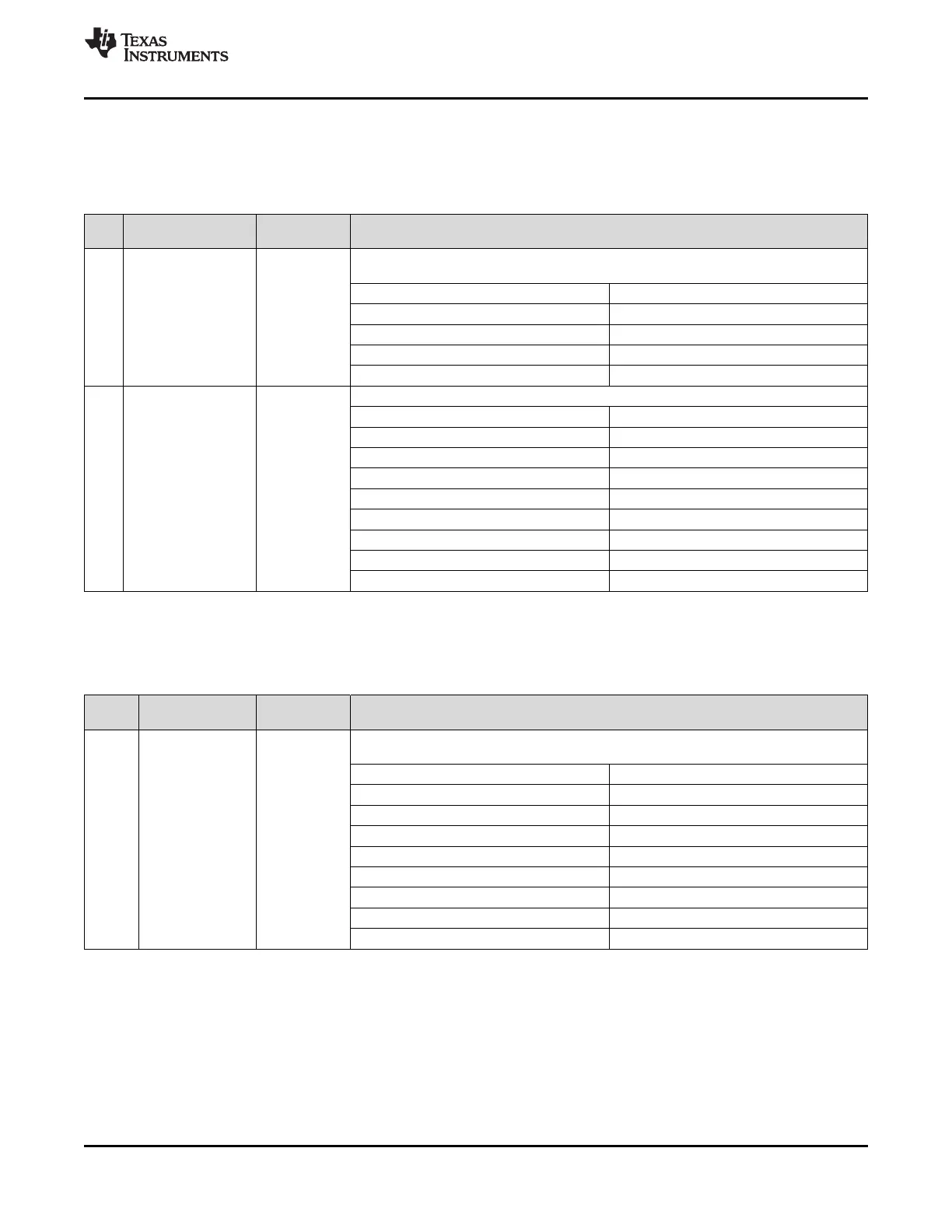

9.7.6.4 DAC_CLK_MULT, DAC_TRIP_HIGH

This register contains the multiplier for the DAC clock counter and the low value at which holdover mode is

entered.

Table 45. Register 0x14E

POR

BIT NAME DESCRIPTION

DEFAULT

This is the multiplier for the DAC_CLK_CNTR which sets the rate at which the DAC value is

tracked.

Field Value DAC Multiplier Value

0 (0x00) 4

7:6 DAC_CLK_MULT 0

1 (0x01) 64

2 (0x02) 1024

3 (0x03) 16384

Voltage from Vcc at which holdover is entered if HOLDOVER_VTUNE_DET is enabled.

Field Value DAC Trip Value

0 (0x00) 1 x Vcc / 64

1 (0x01) 2 x Vcc / 64

2 (0x02) 3 x Vcc / 64

5:0 DAC_TRIP_HIGH 0

3 (0x03) 4 x Vcc / 64

... ...

61 (0x17) 62 x Vcc / 64

62 (0x18) 63 x Vcc / 64

63 (0x19) 64 x Vcc / 64

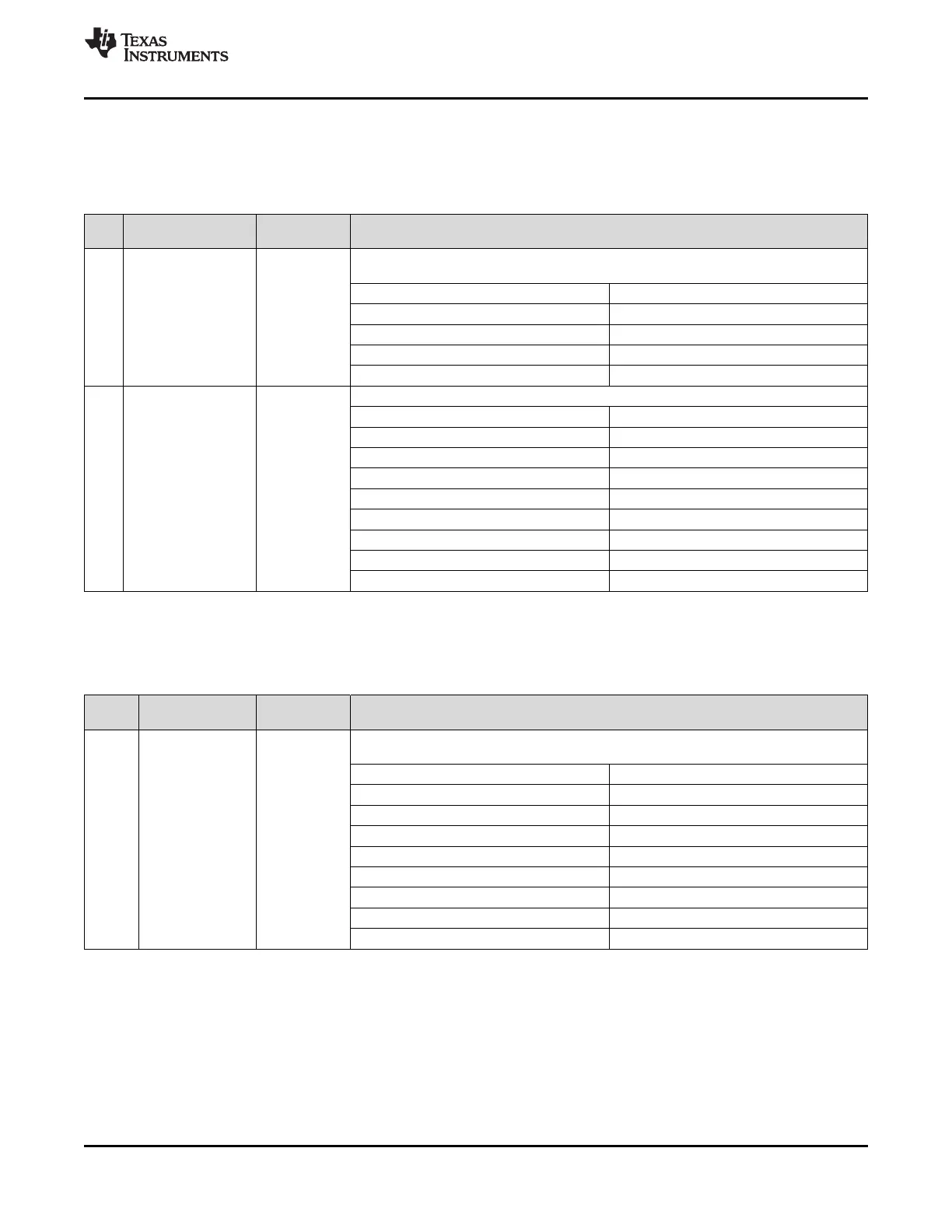

9.7.6.5 DAC_CLK_CNTR

This register contains the value of the DAC when in tracked mode.

Table 46. Register 0x14F

POR

BIT NAME DESCRIPTION

DEFAULT

This with DAC_CLK_MULT set the rate at which the DAC is updated. The update rate is =

DAC_CLK_MULT * DAC_CLK_CNTR / PLL1 PDF

Field Value DAC Value

0 (0x00) 0

1 (0x01) 1

2 (0x02) 2

7:0 DAC_CLK_CNTR 127

3 (0x03) 3

... ...

253 (0xFD) 253

254 (0xFE) 254

255 (0xFF) 255

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 75

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...