LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

9.3 Feature Description

9.3.1 SYNC/SYSREF

The SYNC and SYSREF signals share the same clocking path. To properly use SYNC and/or SYSREF for

JESD204B it is important to understand the SYNC/SYSREF system. Figure 12 illustrates the detailed diagram of

a clock output block with SYNC circuitry included.Figure 13 illustrates the interconnects and highlights some

important registers used in controlling the device for SYNC/SYSREF purposes.

To reset or synchronize a divider, the following conditions must be met:

1. SYNC_EN must be set. This ensures proper operation of the SYNC circuitry.

2. SYSREF_MUX and SYNC_MODE must be set to a proper combination to provide a valid SYNC/SYSREF

signal.

– If SYSREF block is being used, the SYSREF_PD bit must be clear.

– If the SYSREF Pulser is being used, the SYSREF_PLSR_PD bit must be clear.

– For each SDCLKoutY being used for SYSREF, respective SDCLKoutY_PD bits must be cleared.

3. SYSREF_DDLY_PD and DCLKoutX_DDLY_PD bits must be clear to power up the digital delay circuitry

during SYNC as use requires.

4. The SYNC_DISX bit must be clear to allow SYNC/SYSREF signal to divider circuit. The SYSREF_MUX

register selects the SYNC source which resets the SYSREF/CLKoutX dividers provided the corresponding

SYNC_DISX bit is clear.

5. Other bits which impact the operation of SYNC such as SYNC_1SHOT_EN may be set as desired.

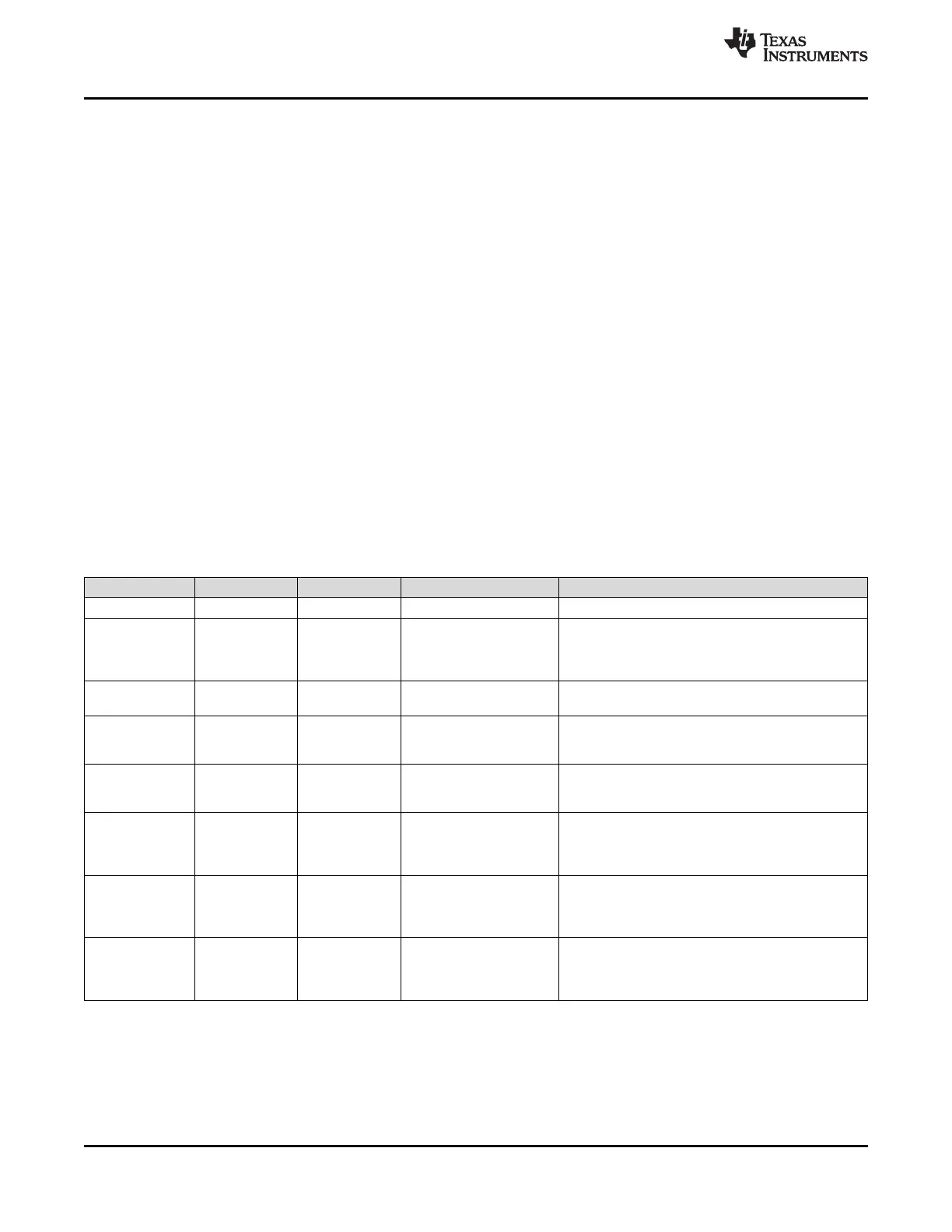

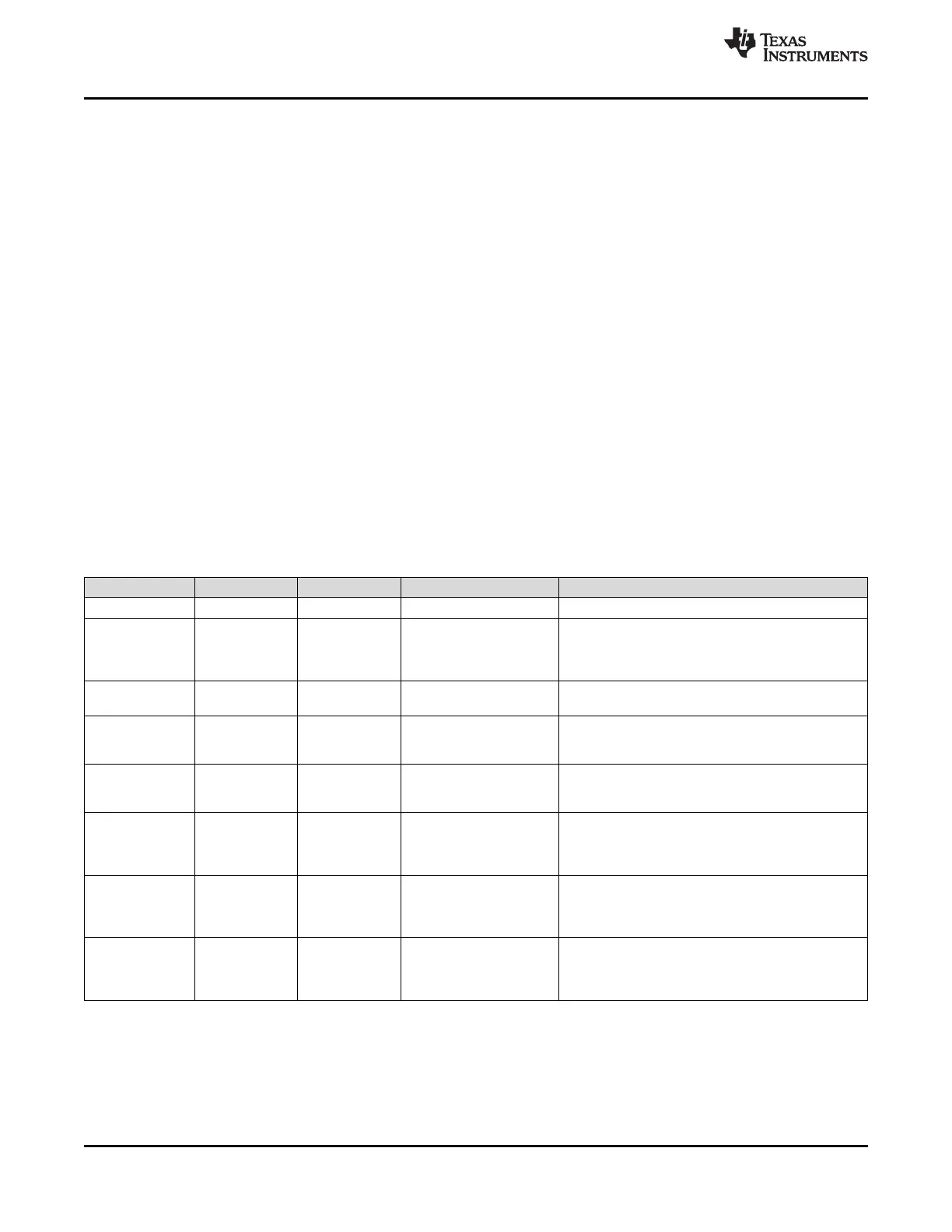

Table 1 illustrates the some possible combinations of SYSREF_MUX and SYNC_MODE.

Table 1. Some Possible SYNC Configurations

NAME SYNC_MODE SYSREF_MUX OTHER DESCRIPTION

SYNC Disabled 0 0 CLKin0_OUT_MUX ≠ 0 No SYNC will occur.

Basic SYNC functionality, SYNC pin polarity is

selected by SYNC_POL.

Pin or SPI SYNC 1 0 CLKin0_OUT_MUX ≠ 0

To achieve SYNC through SPI, toggle the

SYNC_POL bit.

Differential input

0 or 1 0 or 1 CLKin0_OUT_MUX = 0 Differential CLKin0 now operates as SYNC input.

SYNC

Produce SYSREF_PULSE_CNT programmed

JESD204B Pulser SYSREF_PULSE_CNT

2 2 number of pulses on pin transition. SYNC_POL can

on pin transition. sets pulse count

be used to cause SYNC via SPI.

JESD204B Pulser

SYSREF_PULSE_CNT Programming SYSREF_PULSE_CNT register starts

on SPI 3 2

sets pulse count sending the number of pulses.

programming.

SYSREF operational,

SYSREF Divider as Allows precise SYNC for n-bit frame training patterns

Re-clocked SYNC 1 1

required for training frame for non-JESD converters such as LM97600.

size.

When SYNC pin is asserted, continuous SYSERF

External SYSREF SYSREF_REQ_EN = 1 pulses occur. Turning on and off of the pulses is

0 2

request Pulser powered up synchronized to prevent runt pulses from occurring on

SYSREF.

SYSREF_PD = 0

Continuous SYSREF_DDLY_PD = 0

X 3 Continuous SYSREF signal.

SYSREF SYSREF_PLSR_PD = 1

(1)

(1) SDCLKoutY_PD = 0 as required per SYSREF output. This applies to any SYNC or SYSREF output on SDCLKoutY when

SDCLKoutY_MUX = 1 (SYSREF output)

36 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...