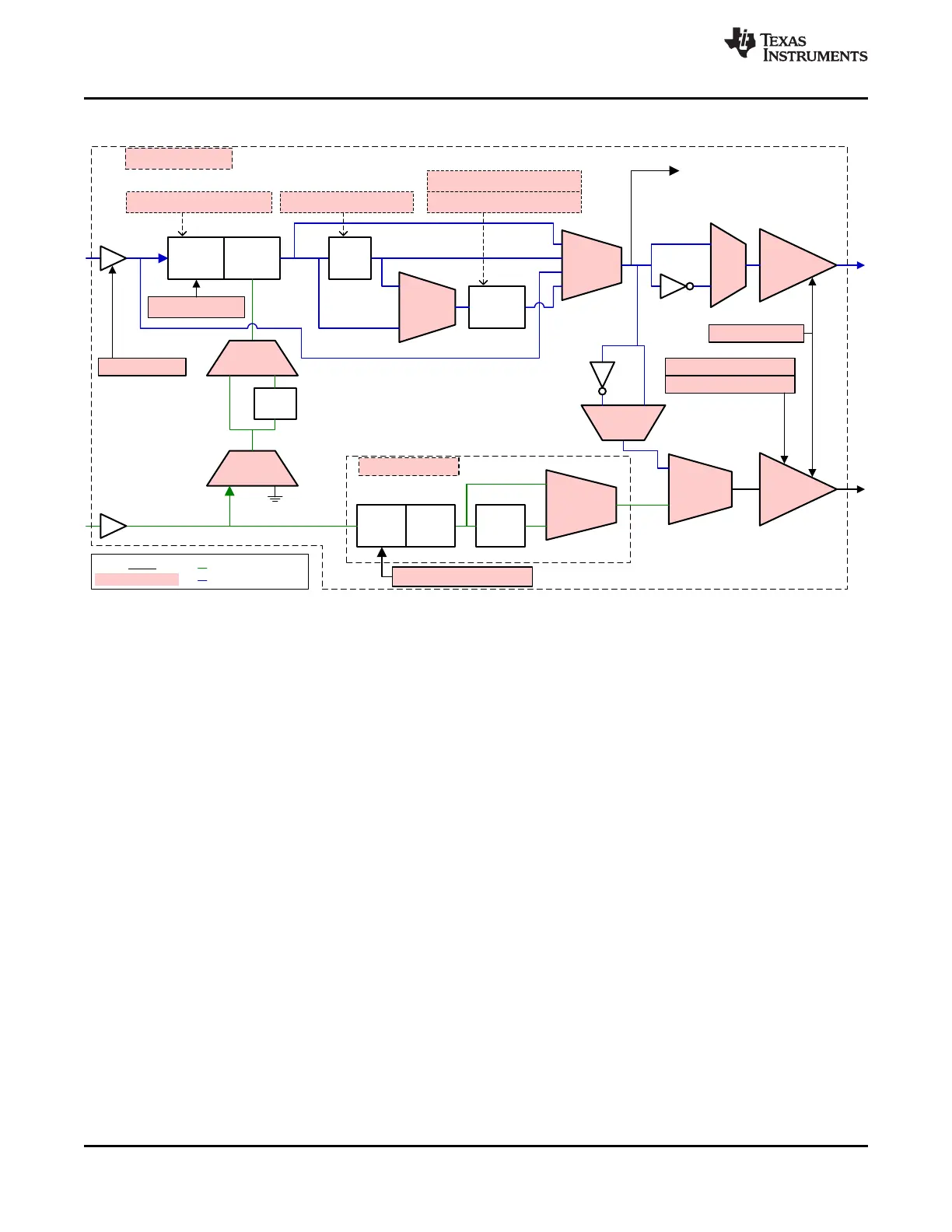

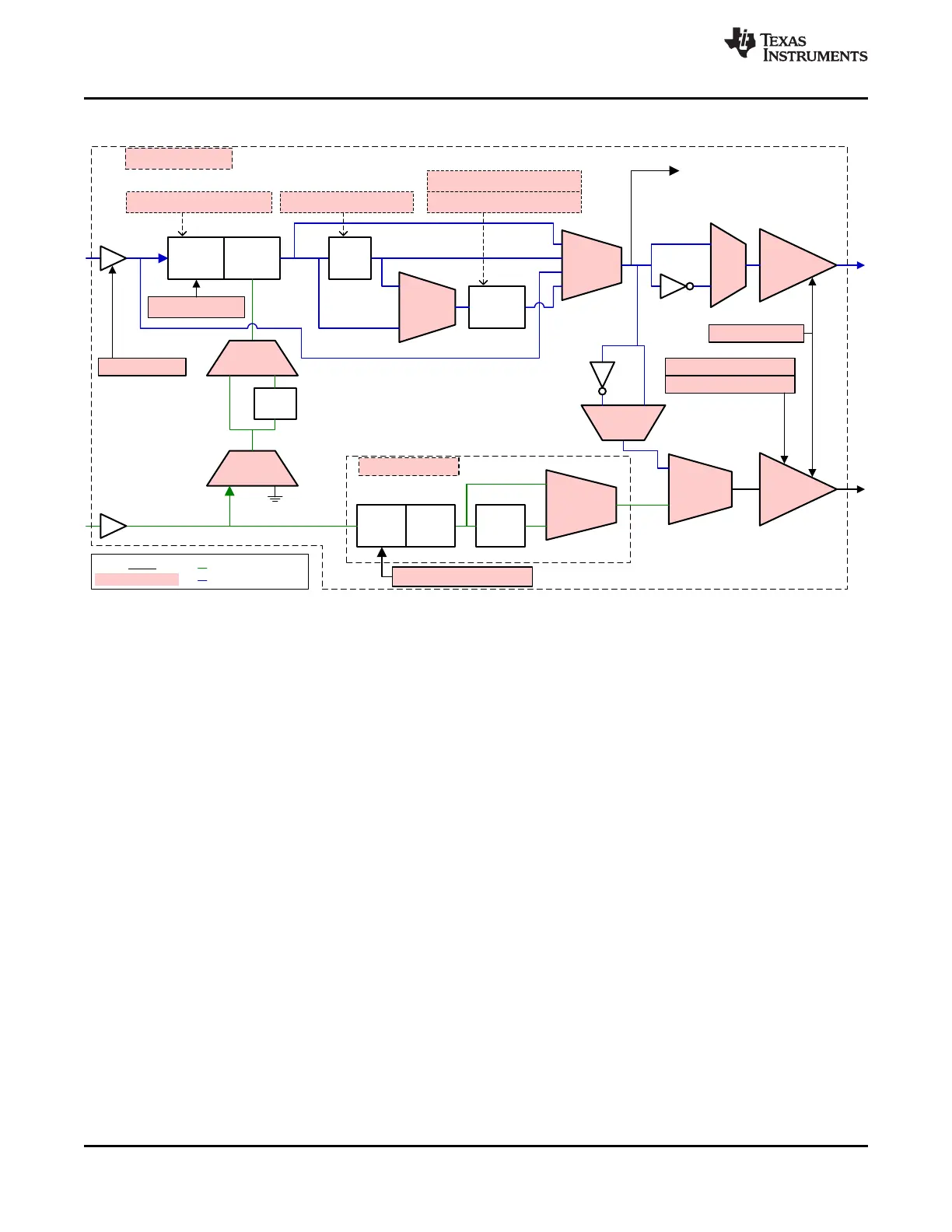

DDLY

(4 to 32)

Divider

(1 to 32)

SYNC_

DISX

Analog

DLY

Digital

DLY

VCO

SYSREF/SYNC

DCLKout0, 2, 4, 6, 8, 10, 12

SDCLKout1, 3, 5, 7, 9, 11, 13

SDCLKoutY_DIS_MODE

One

Shot

SYNC_

1SHOT_EN

DDDLYdX_EN

DCLKoutX

_MUX

HS/

DCC

Analog

DLY

SDCLKoutY

_ADLY_EN

DCLKoutX_

FMT

SDCLKoutY

_MUX

DCLKoutX

_ADLY

_MUX

SDCLKoutY_

FMT

SYSREF_CLR

Half

Step

DCLKoutX_ADLY_PD

DCLKoutX_ADLYg_PDDCLKoutX_HSg_PD

SDCLKoutY_PD

CLKoutX_Y_PD

SDCLKoutY

_POL

DCLKoutX

_POL

DCLKout6/8 to FB_MUX

SYSREF_GBL_PD

DCLKoutX_DDLY_PD

CLKoutX_Y_ODL

CLKoutX_Y_IDL

SPI Register

Legend

SYSREF/SYNC Clock

VCO/Distribution Clock

LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

Functional Block Diagram (continued)

Figure 12. Device and SYSREF Clock Output Block

34 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...