LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

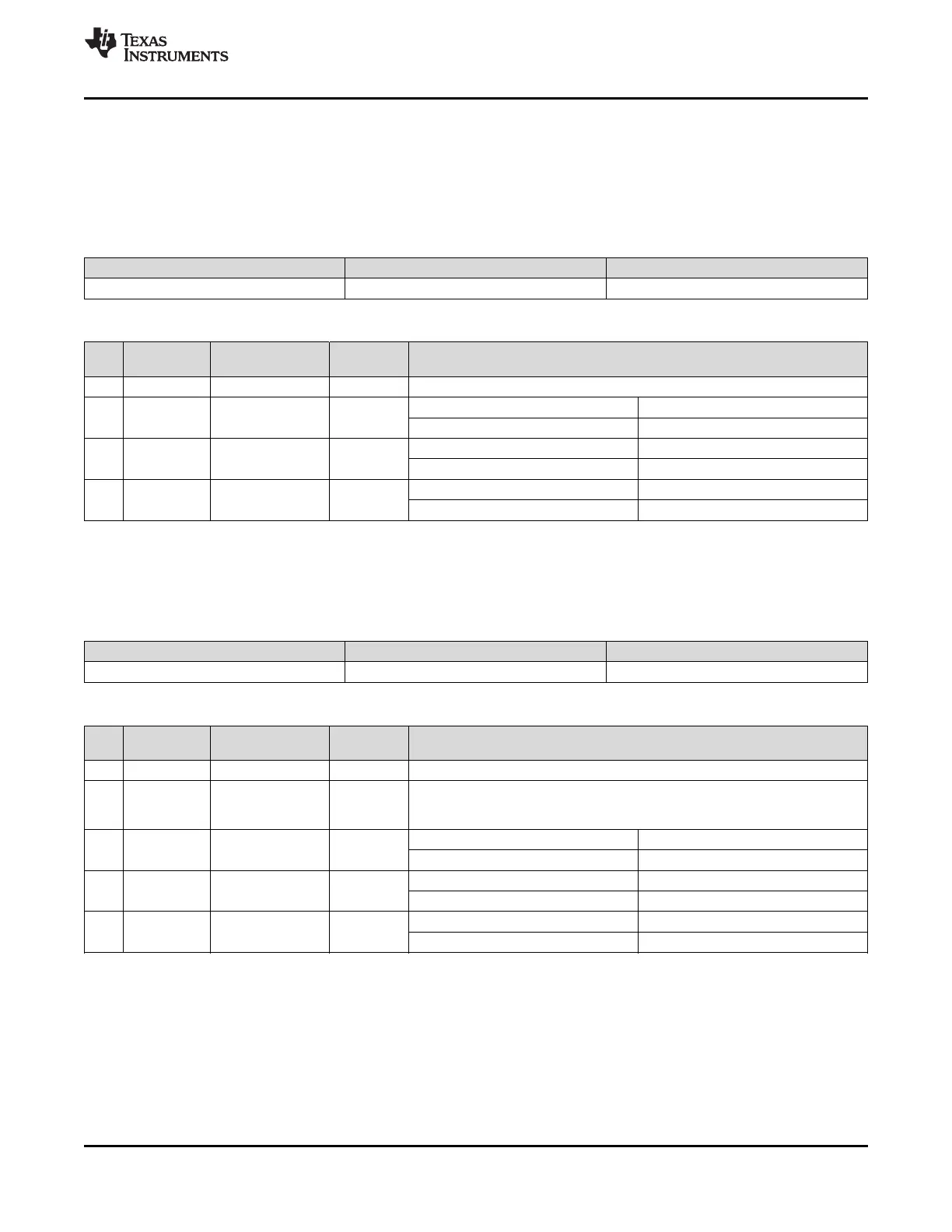

9.7.8.3 PLL2_N_CAL

PLL2_N_CAL[17:0]

PLL2 never uses 0-delay during frequency calibration. These registers contain the value of the PLL2 N divider

used with PLL2 pre-scaler during calibration for cascaded 0-delay mode. Once calibration is complete, PLL2 will

use PLL2_N value. Cascaded 0-delay mode occurs when PLL2_NCLK_MUX = 1.

Table 64. Register 0x162

MSB — LSB

0x163[1:0] 0x164[7:0] 0x165[7:0]

Table 65. Registers 0x163, 0x164, and 0x165

POR

BIT REGISTERS NAME DESCRIPTION

DEFAULT

7:2 0x163 NA 0 Reserved

Field Value Divide Value

PLL2_N

1:0 0x163 0

_CAL[17:16]

0 (0x00) Not Valid

1 (0x01) 1

7:0 0x164 PLL2_N_CAL[15:8] 0

2 (0x02) 2

... ...

7:0 0x165 PLL2_N_CAL[7:0] 12

262,143 (0x3FFFF) 262,143

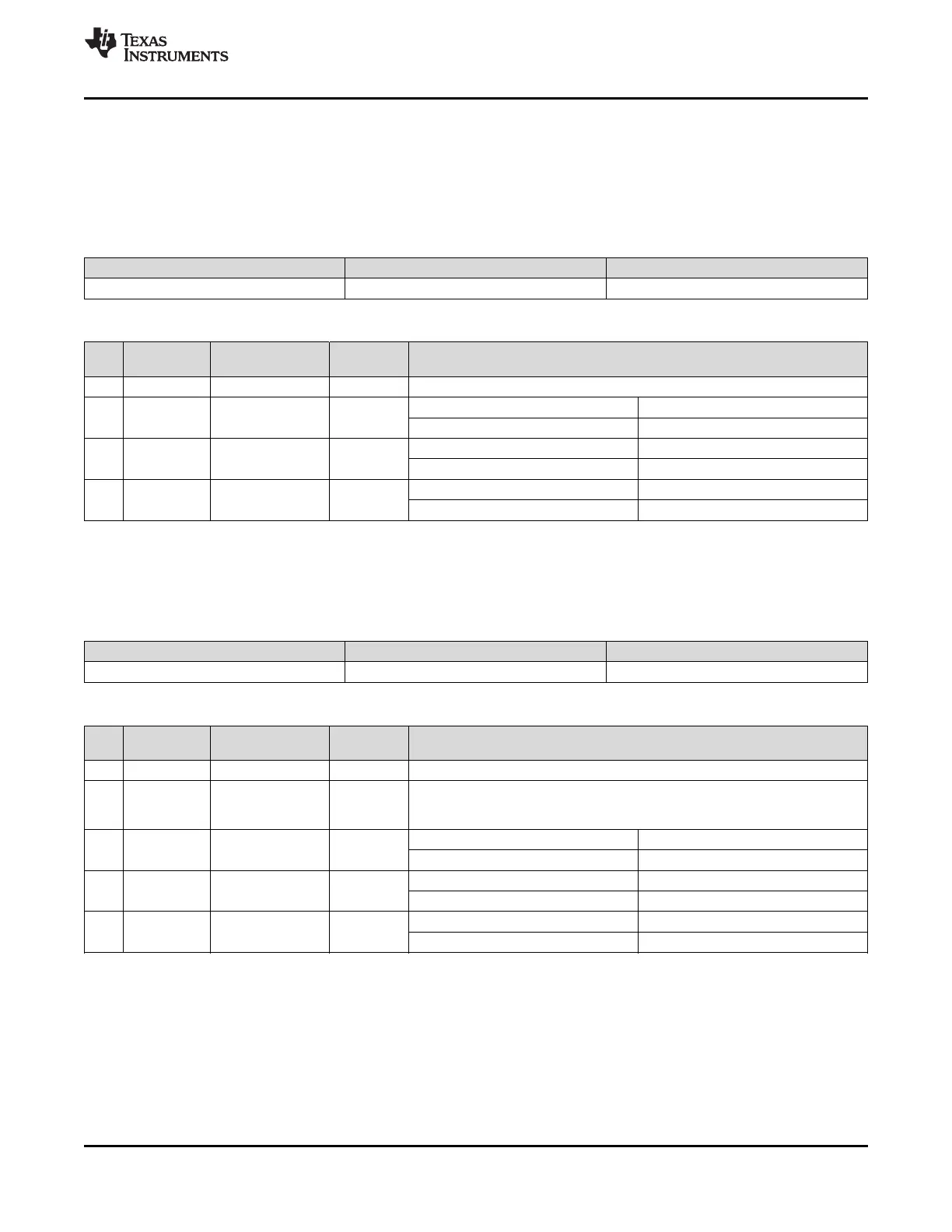

9.7.8.4 PLL2_FCAL_DIS, PLL2_N

This register disables frequency calibration and sets the PLL2 N divider value. Programming register 0x168

starts a VCO calibration routine if PLL2_FCAL_DIS = 0.

Table 66. PLL2_N[17:0]

MSB — LSB

0x166[1:0] 0x167[7:0] 0x168[7:0]

Table 67. Registers 0x166, 0x167, and 0x168

POR

BIT REGISTERS NAME DESCRIPTION

DEFAULT

7:3 0x166 NA 0 Reserved

This disables the PLL2 frequency calibration on programming register 0x168.

2 0x166 PLL2_FCAL_DIS 0 0: Frequency calibration enabled

1: Frequency calibration disabled

Field Value Divide Value

1:0 0x166 PLL2_N[17:16] 0

0 (0x00) Not Valid

1 (0x01) 1

7:0 0x167 PLL2_N[15:8] 0

2 (0x02) 2

... ...

7:0 0x168 PLL2_N[7:0] 12

262,143 (0x3FFFF) 262,143

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 85

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...