LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

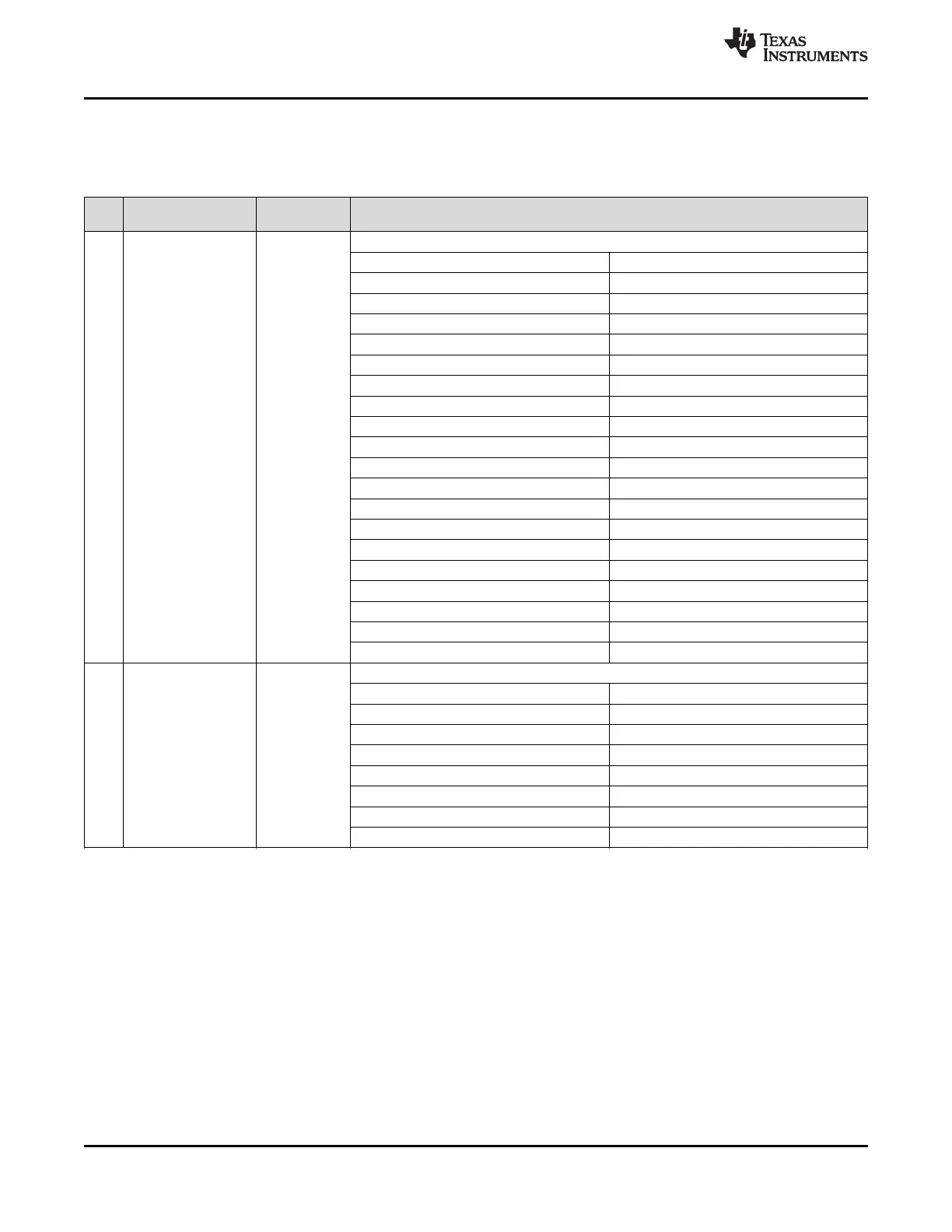

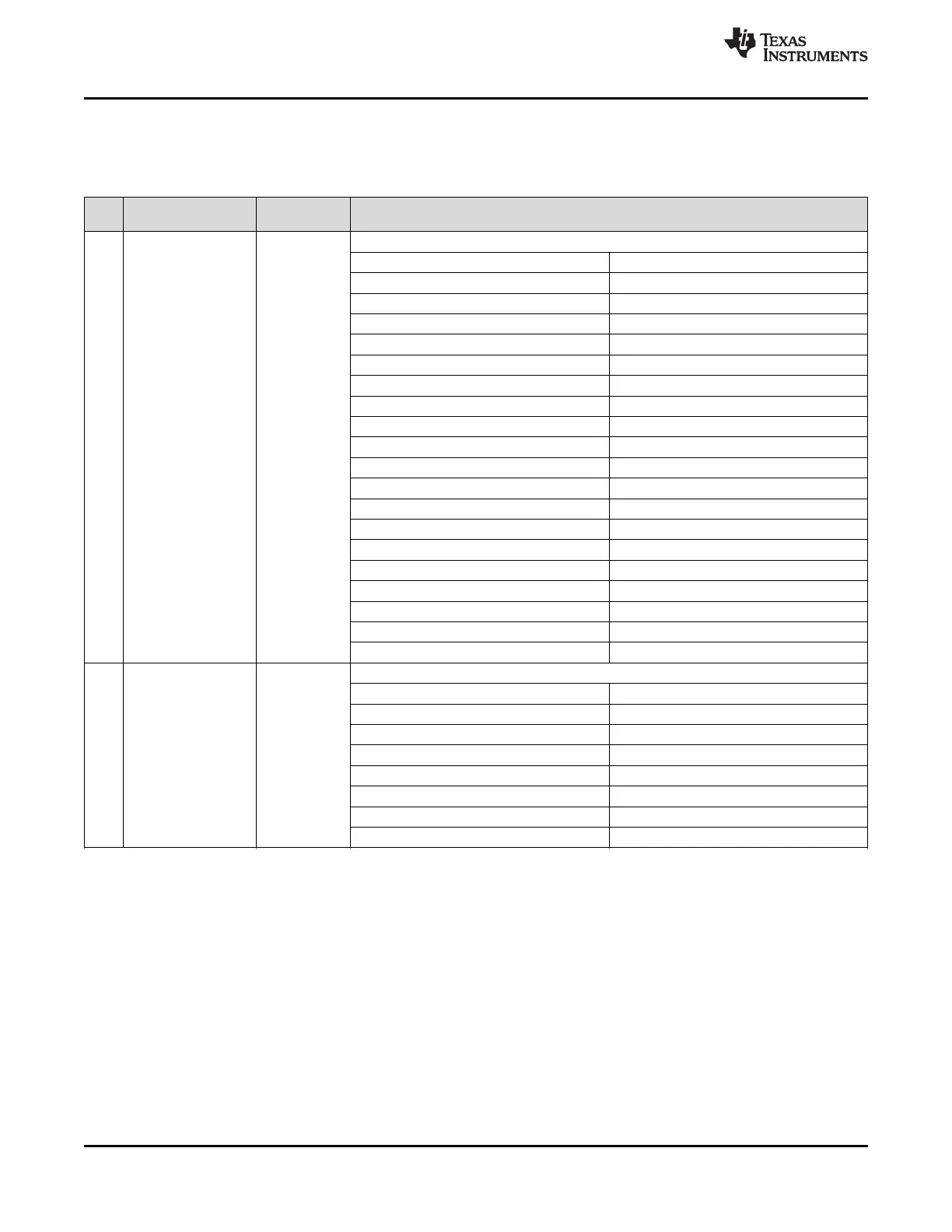

9.7.7.8 PLL1_LD_MUX, PLL1_LD_TYPE

This register configures the PLL1 LD pin.

Table 60. Register 0x15F

POR

BIT NAME DESCRIPTION

DEFAULT

This sets the output value of the Status_LD1 pin.

Field Value MUX Value

0 (0x00) Logic Low

1 (0x01) PLL1 DLD

2 (0x02) PLL2 DLD

3 (0x03) PLL1 & PLL2 DLD

4 (0x04) Holdover Status

5 (0x05) DAC Locked

6 (0x06) Reserved

7 (0x07) SPI Readback

7:3 PLL1_LD_MUX 1 8 (0x08) DAC Rail

9 (0x09) DAC Low

10 (0x0A) DAC High

11 (0x0B) PLL1_N

12 (0x0C) PLL1_N/2

13 (0x0D) PLL2_N

14 (0x0E) PLL2_N/2

15 (0x0F) PLL1_R

16 (0x10) PLL1_R/2

17 (0x11) PLL2_R

(1)

18 (0x12) PLL2_R/2

(1)

Sets the IO type of the Status_LD1 pin.

Field Value TYPE

0 (0x00) Reserved

1 (0x01) Reserved

2:0 PLL1_LD_TYPE 6 2 (0x02) Reserved

3 (0x03) Output (push-pull)

4 (0x04) Output inverted (push-pull)

5 (0x05) Reserved

6 (0x06) Output (open drain)

(1) Only valid when PLL2_LD_MUX is not set to 2 (PLL2_DLD) or 3 (PLL1 & PLL2 DLD).

82 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...