LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

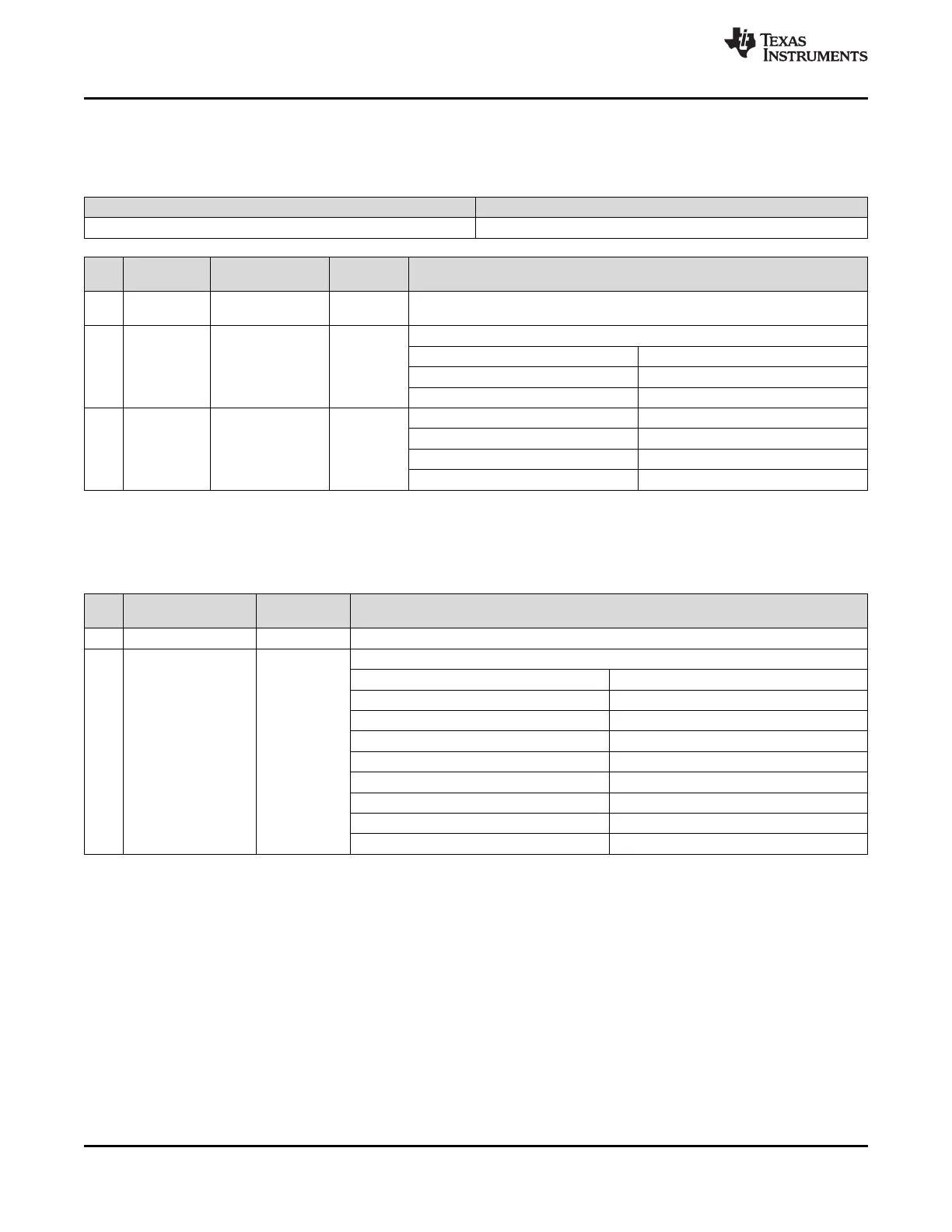

9.7.6.2 MAN_DAC[9:8], MAN_DAC[7:0]

These registers set the value of the DAC in holdover mode when used manually.

Table 43. MAN_DAC[9:0]

MSB LSB

0x14B[1:0] 0x14C[7:0]

POR

BIT REGISTERS NAME DESCRIPTION

DEFAULT

See LOS_TIMEOUT, LOS_EN, TRACK_EN, HOLDOVER_FORCE,

7:2 0x14B

MAN_DAC_EN, MAN_DAC[9:8] for information on these bits.

Sets the value of the manual DAC when in manual DAC mode.

Field Value DAC Value

1:0 0x14B MAN_DAC[9:8] 2

0 (0x00) 0

1 (0x01) 1

2 (0x02) 2

... ...

7:0 0x14C MAN_DAC[7:0] 0

1022 (0x3FE) 1022

1023 (0x3FF) 1023

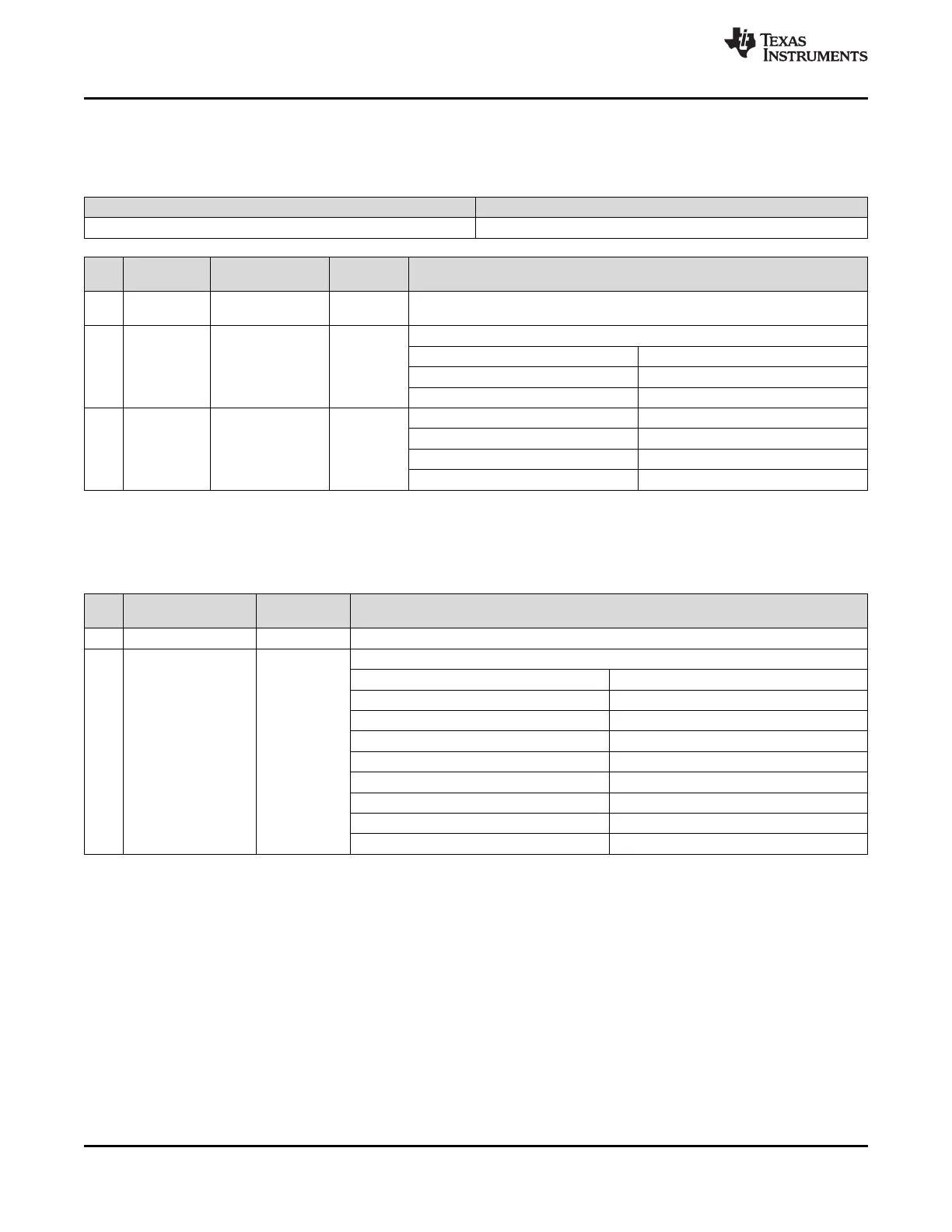

9.7.6.3 DAC_TRIP_LOW

This register contains the high value at which holdover mode is entered.

Table 44. Register 0x14D

POR

BIT NAME DESCRIPTION

DEFAULT

7:6 NA 0 Reserved

Voltage from GND at which holdover is entered if HOLDOVER_VTUNE_DET is enabled.

Field Value DAC Trip Value

0 (0x00) 1 x Vcc / 64

1 (0x01) 2 x Vcc / 64

2 (0x02) 3 x Vcc / 64

5:0 DAC_TRIP_LOW 0

3 (0x03) 4 x Vcc / 64

... ...

61 (0x17) 62 x Vcc / 64

62 (0x18) 63 x Vcc / 64

63 (0x19) 64 x Vcc / 64

74 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...