Hardware-Based Protection

www.ti.com

26

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Protections

0010 = 14 mv

0011 = 17 mv

0100 = 19 mv

0101 = 25 mv

0110 = 28 mv

0111 = 31 mv

1000 = 31 mv

1001 = 33 mv

1010 = 36 mv

1011 = 39 mv

1100 = 42 mv

1101 = 44 mv

1110 = 47 mv

1111 = 50 mv

3.6.2 Short Circuit in Discharge Protection

The device has a hardware-based short circuit in discharge protection with adjustable current and delay.

See Section 3.1.4 for additional FET action options.

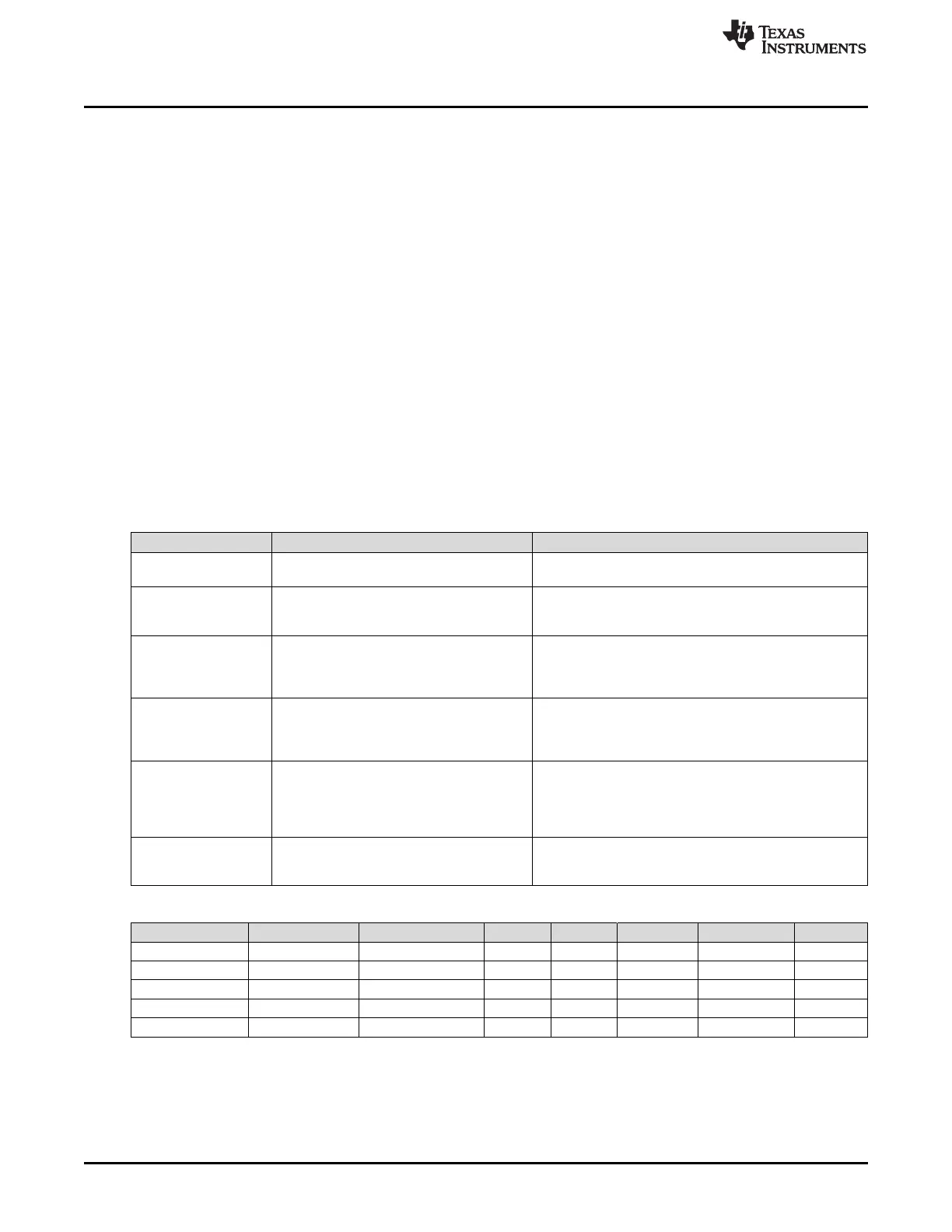

Status Condition Action

Normal

Current() > (ASCD Threshold and

Delay[2:0]/R

SENSE

)

SafetyAlert()[ASCDL] = 0, if ASCDL counter = 0

Alert ASCDL counter > 0

SafetyAlert()[ASCDL] = 1

Decrement ASCDL counter by one after each

SCD:Counter Dec Delay period

Trip

Current() continuous ≤ (ASCD Threshold

and Delay[2:0]/R

SENSE

) for ASCD Threshold

and Delay[7:4] duration

SafetyStatus()[ASCD] = 1

OperationStatus()[XDSG] = 1

DSG FET is disabled.

Increment ASCDL counter

Latch ASCD counter ≥ ASCD:Latch Limit

SafetyStatus()[ASCD] = 0

SafetyStatus()[ASCDL] = 1

OperationStatus()[XDSG] = 1

DSG FET is disabled.

Recovery

SafetyStatus()[ASCD] = 1 for

ASCD:Recovery time

OR

If Protection Configuration [LPEN] = 1

AND AFEStatus()[LOAD_PRESENT] = 0

SafetyStatus()[ASCD] = 0

OperationStatus()[XDSG] = 0

DSG FET returns to normal if SafetyStatus()[ASCDL] = 0.

Latch Reset

SafetyStatus()[ASCDL] = 1

for ASCD:Reset time

SafetyStatus()[ASCDL] = 0

OperationStatus()[XDSG] = 0

DSG FET returns to normal if SafetyStatus()[ASCD] = 0.

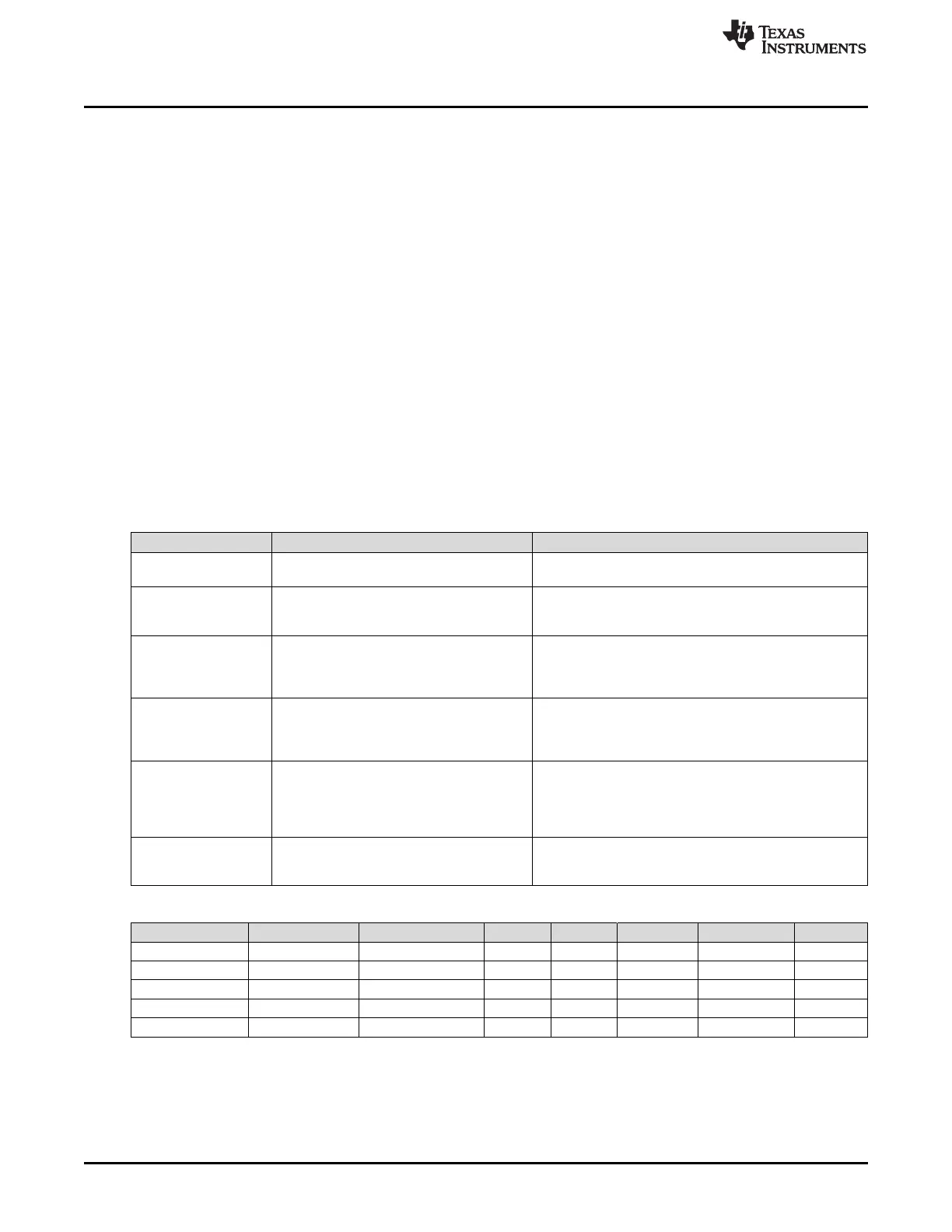

Class Subclass Name Type Min Max Default Unit

Protections ASCD Threshold and Delay H1 0x00 0xFF 0x00 —

Protections ASCD Latch Limit U1 0 255 0 counts

Protections ASCD Counter Dec Delay U1 0 255 10 s

Protections ASCD Recovery U1 0 255 5 s

Protections ASCD Reset U1 0 255 15 s

This register is representative of the bq769x0 PROTECT 1 register.

Loading...

Loading...