LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

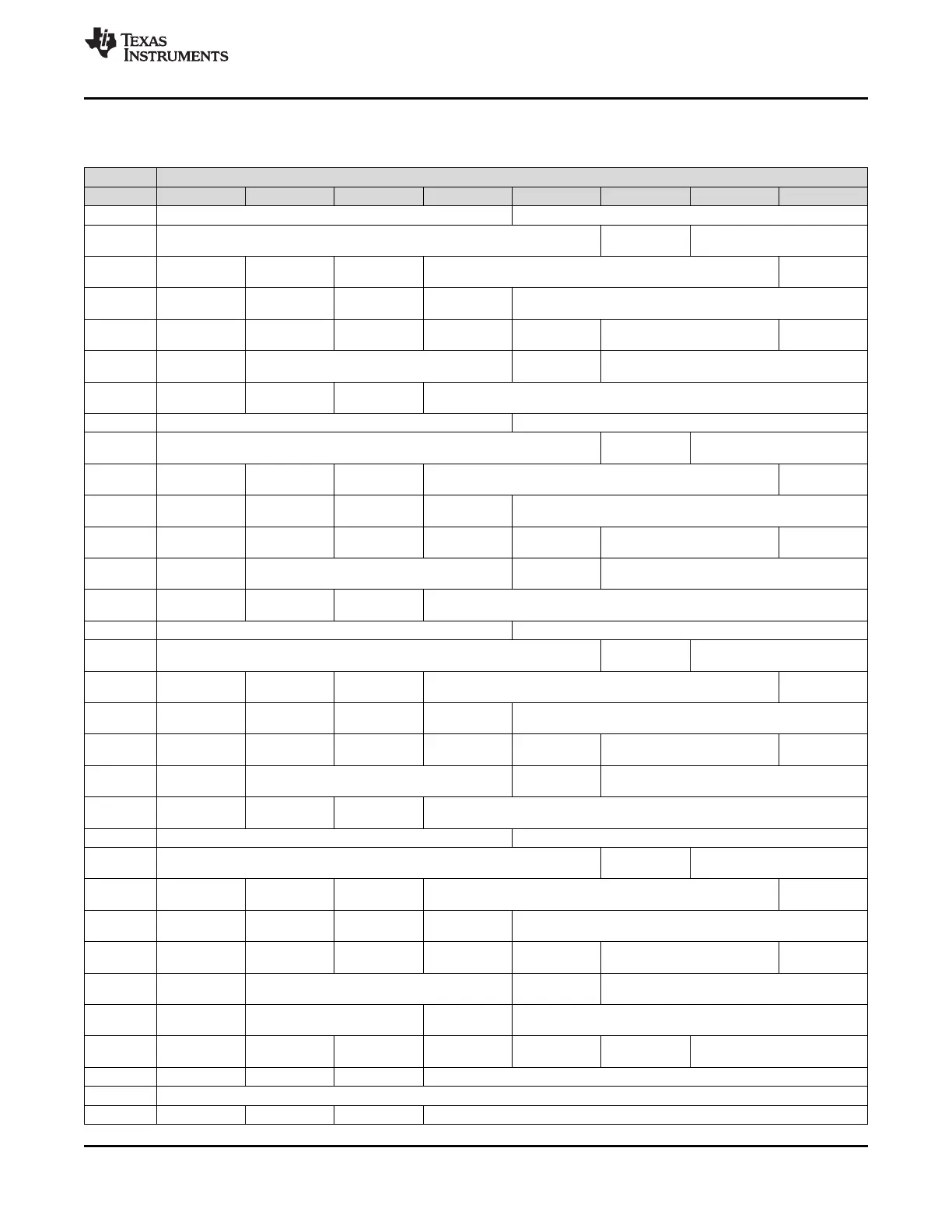

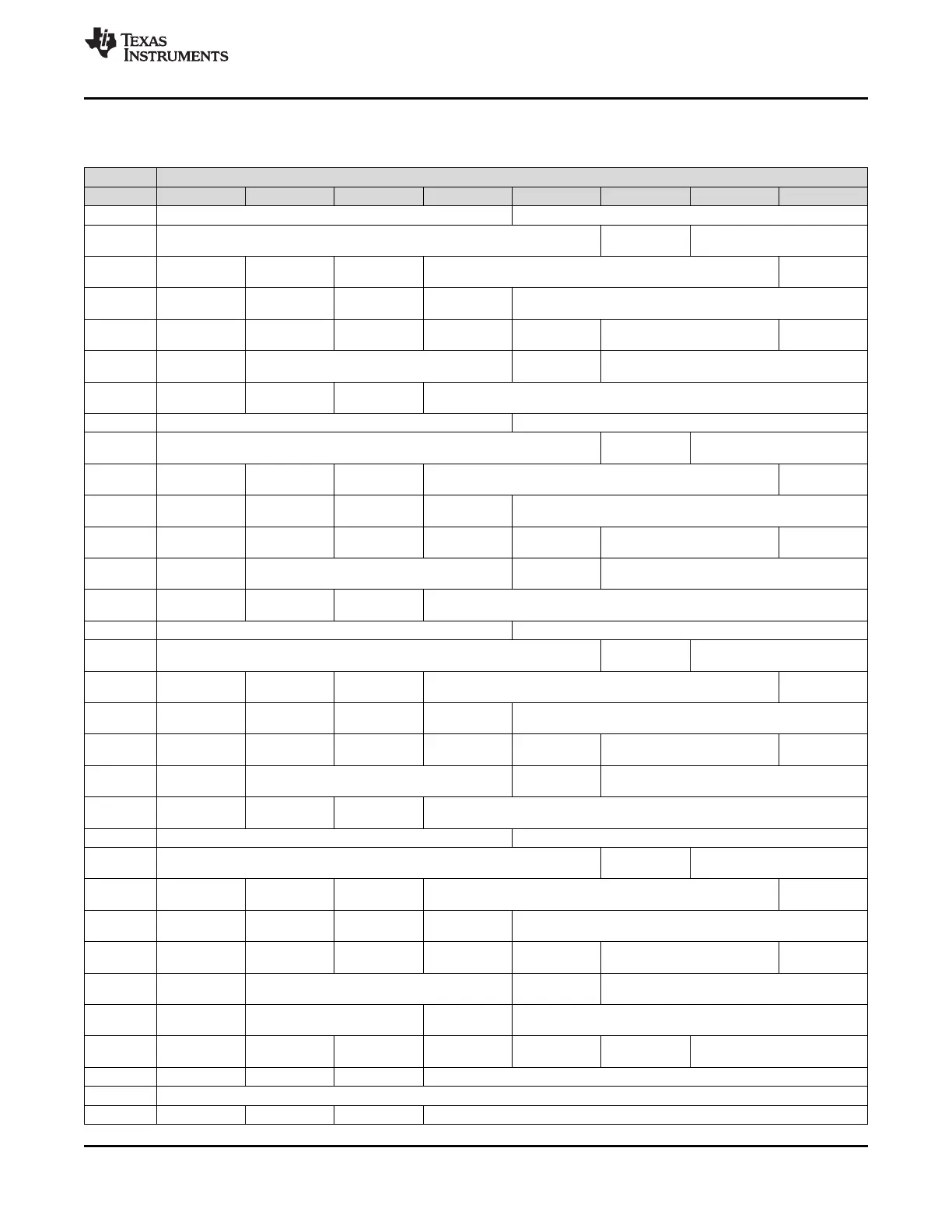

Register Maps (continued)

Table 8. LMK0482x Register Map (continued)

ADDRESS DATA

[11:0] 7 6 5 4 3 2 1 0

0x119 DCLKout6_DDLY_CNTH DCLKout6_DDLY_CNTL

DCLKout6_

0x11B DCLKout6_ADLY DCLKout6_MUX

ADLY_MUX

DCLKout6 SDCLKout7 SDCLKout7

0x11C 0 SDCLKout7_DDLY

_HS _MUX _HS

SDCLKout7

0x11D 0 0 0 SDCLKout7_ADLY

_ ADLY_EN

DCLKout6 DCLKout6 DCLKout6 DCLKout6 CLKout6_7 SDCLKout7

0x11E SDCLKout7_DIS_MODE

_ DDLY_PD _ HSg_PD _ ADLYg_PD _ADLY _PD _PD _PD

SDCLKout7 CLKout7 DCLKout6

0x11F CLKout6_FMT

_POL _FMT _POL

CLKout8_9 CLKout8_9

0x120 0 DCLKout8_DIV

_ODL _IDL

0x121 DCLKout8_DDLY_CNTH DCLKout8_DDLY_CNTL

DCLKout8

0x123 DCLKout8_ADLY DCLKout8_MUX

_ ADLY_MUX

DCLKout8 SDCLKout9 SDCLKout9

0x124 0 SDCLKout9_DDLY

_HS _MUX _HS

SDCLKout9

0x125 0 0 0 SDCLKout9_ADLY

_ ADLY_EN

DCLKout8 DCLKout8 DCLKout8 DCLKout8 CLKout8_9 SDCLKout9

0x126 SDCLKout9_DIS_MODE

_ DDLY_PD _ HSg_PD _ ADLYg_PD _ADLY _PD _PD _PD

SDCLKout9 DCLKout8

0x127 CLKout9_FMT CLKout8_FMT

_POL _POL

CLKout10 CLKout10

0x128 0 DCLKout10_DIV

_11 _ODL _11_IDL

0x129 DCLKout10_DDLY_CNTH DCLKout10_DDLY_CNTL

DCLKout10

0x12B DCLKout10_ADLY DCLKout10_MUX

_ ADLY_MUX

DCLKout10 SDCLKout11 SDCLKout11

0x12C 0 SDCLKout11_DDLY

_HS _MUX _HS

SDCKLout11

0x12D 0 0 0 SDCLKout11_ADLY

_ ADLY_EN

DCLKout10 DCLKout10 DLCLKout10 DCLKout10 CLKout10 SDCLKout11

0x12E SDCLKout11_DIS_MODE

_ DDLY_PD _ HSg_PD _ ADLYg_PD _ ADLY_PD _11_PD _PD

SDCLKout11 DCLKout10

0x12F CLKout11_FMT CLKout10_FMT

_POL _POL

CLKout12 CLKout12

0x130 0 DCLKout12_DIV

_13 _ODL _13_IDL

0x131 DCLKout12_DDLY_CNTH DCLKout12_DDLY_CNTL

DCLKout12_

0x133 DCLKout12_ADLY DCLKout12_MUX

ADLY_MUX

DCLKout12 SDCLKout13 SDCLKout13

0x134 0 SDCLKout13_DDLY

_HS _MUX _HS

SDCLKout13

0x135 0 0 0 SDCLKout13_ADLY

_ ADLY_EN

DCLKout12 DCLKout12 DCLKout12 DCLKout12 CLKout12 SDCLKout13

0x136 SDCLKout13_DIS_MODE

_ DDLY_PD _ HSg_PD _ ADLYg_PD _ ADLY_PD _13_PD _PD

SDCLKout13 DCLKout12

0x137 CLKout13_FMT CLKout12_FMT

_POL _POL

OSCout

0x138 0 VCO_MUX OSCout_FMT

_MUX

SYSREF_

0x139 0 0 0 0 0 SYSREF_MUX

CLKin0_MUX

0x13A 0 0 0 SYSREF_DIV[12:8]

0x13B SYSREF_DIV[7:0]

0x13C 0 0 0 SYSREF_DDLY[12:8]

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 51

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...