LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

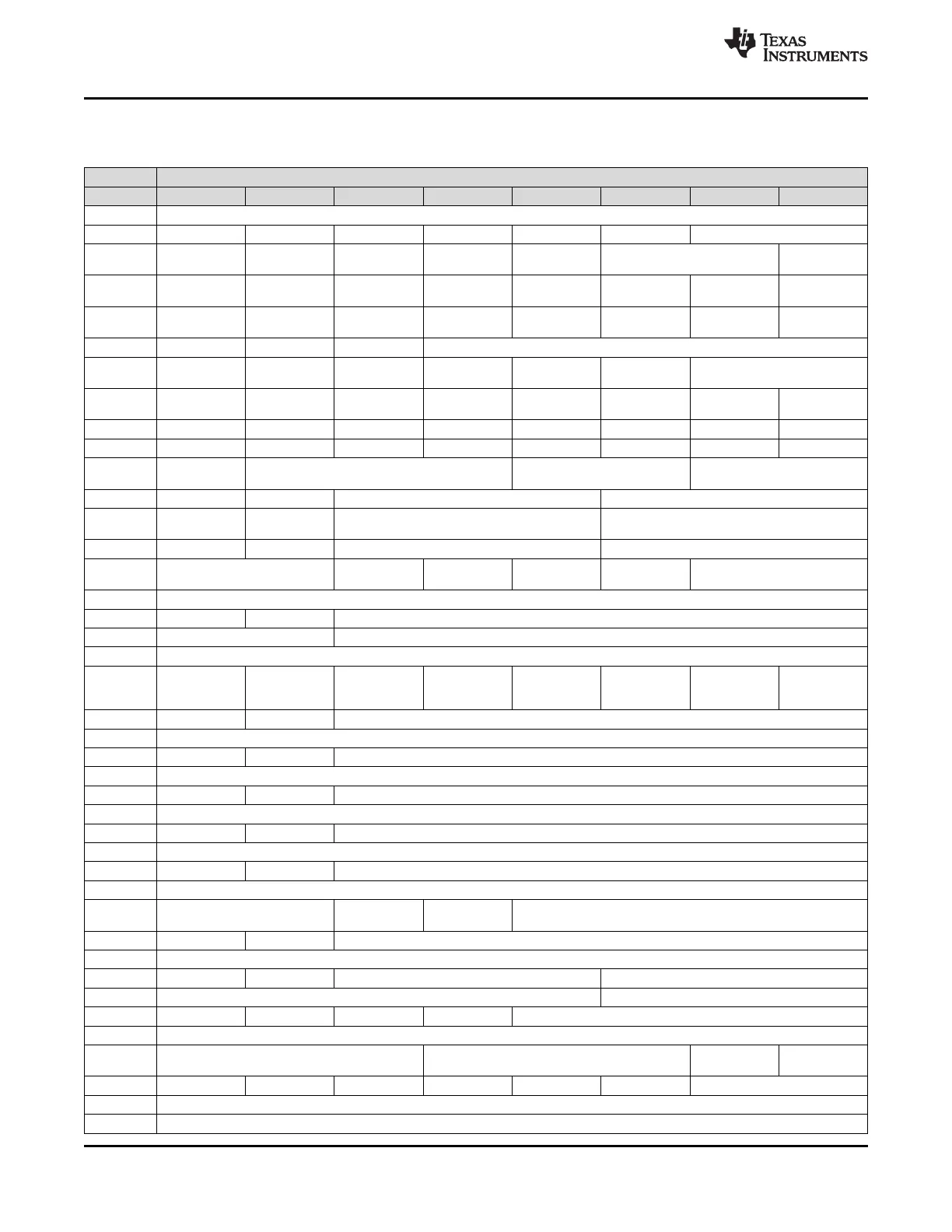

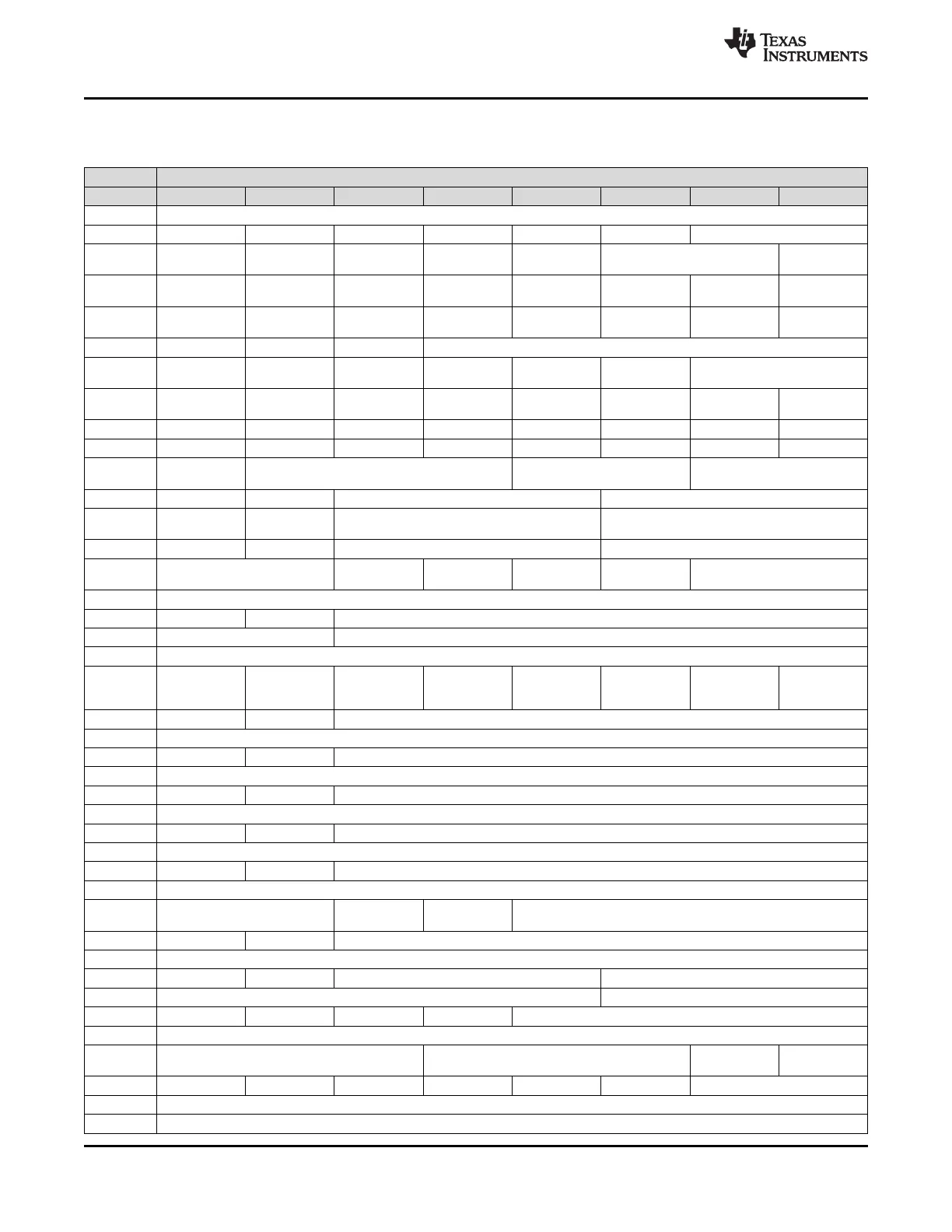

Register Maps (continued)

Table 8. LMK0482x Register Map (continued)

ADDRESS DATA

[11:0] 7 6 5 4 3 2 1 0

0x13D SYSREF_DDLY[7:0]

0x13E 0 0 0 0 0 0 SYSREF_PULSE_CNT

PLL2_NCLK PLL1_NCLK FB_MUX

0x13F 0 0 0 FB_MUX

_MUX _MUX _EN

SYSREF_GBL SYSREF SYSREF

0x140 PLL1_PD VCO_LDO_PD VCO_PD OSCin_PD SYSREF_PD

_PD _DDLY_PD _PLSR_PD

DDLYd_ DDLYd12 DDLYd10

0x141 DDLYd7_EN DDLYd6_EN DDLYd4_EN DDLYd2_EN DDLYd0_EN

SYSREF_EN _EN _EN

0x142 0 0 0 DDLYd_STEP_CNT

SYSREF_DDLY SYNC_1SHOT SYNC_PLL2 SYNC_PLL1

0x143 SYNC_POL SYNC_EN SYNC_MODE

_CLR _EN _DLD _DLD

SYNC

0x144 SYNC_DIS12 SYNC_DIS10 SYNC_DIS8 SYNC_DIS6 SYNC_DIS4 SYNC_DIS2 SYNC_DIS0

_DISSYSREF

0x145 0 1 1 1 1 1 1 1

0x146 0 0 CLKin2_EN CLKin1_EN CLKin0_EN CLKin2_TYPE CLKin1_TYPE CLKin0_TYPE

CLKin_SEL

0x147 CLKin_SEL_MODE CLKin1_OUT_MUX CLKin0_OUT_MUX

_POL

0x148 0 0 CLKin_SEL0_MUX CLKin_SEL0_TYPE

SDIO_RDBK

0x149 0 CLKin_SEL1_MUX CLKin_SEL1_TYPE

_TYPE

0x14A 0 0 RESET_MUX RESET_TYPE

HOLDOVER MAN_DAC

0x14B LOS_TIMEOUT LOS_EN TRACK_EN MAN_DAC[9:8]

_ FORCE _EN

0x14C MAN_DAC[7:0]

0x14D 0 0 DAC_TRIP_LOW

0x14E DAC_CLK_MULT DAC_TRIP_HIGH

0x14F DAC_CLK_CNTR

HOLDOVER

CLKin HOLDOVER HOLDOVER HOLDOVER HOLDOVER

0x150 0 0 _HITLESS

_OVERRIDE _ PLL1_DET _LOS _DET _VTUNE_DET _EN

_SWITCH

0x151 0 0 HOLDOVER_DLD_CNT[13:8]

0x152 HOLDOVER_DLD_CNT[7:0]

0x153 0 0 CLKin0_R[13:8]

0x154 CLKin0_R[7:0]

0x155 0 0 CLKin1_R[13:8]

0x156 CLKin1_R[7:0]

0x157 0 0 CLKin2_R[13:8]

0x158 CLKin2_R[7:0]

0x159 0 0 PLL1_N[13:8]

0x15A PLL1_N[7:0]

PLL1 PLL1

0x15B PLL1_WND_SIZE PLL1_CP_GAIN

_CP_TRI _CP_POL

0x15C 0 0 PLL1_DLD_CNT[13:8]

0x15D PLL1_DLD_CNT[7:0]

0x15E 0 0 PLL1_R_DLY PLL1_N_DLY

0x15F PLL1_LD_MUX PLL1_LD_TYPE

0x160 0 0 0 0 PLL2_R[11:8]

0x161 PLL2_R[7:0]

PLL2 PLL2

0x162 PLL2_P OSCin_FREQ

_XTAL_EN _REF_2X_EN

0x163 0 0 0 0 0 0 PLL2_N_CAL[17:16]

0x164 PLL2_N_CAL[15:8]

0x165 PLL2_N_CAL[7:0]

52 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...