ZCU102 Evaluation Board User Guide www.xilinx.com 24

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

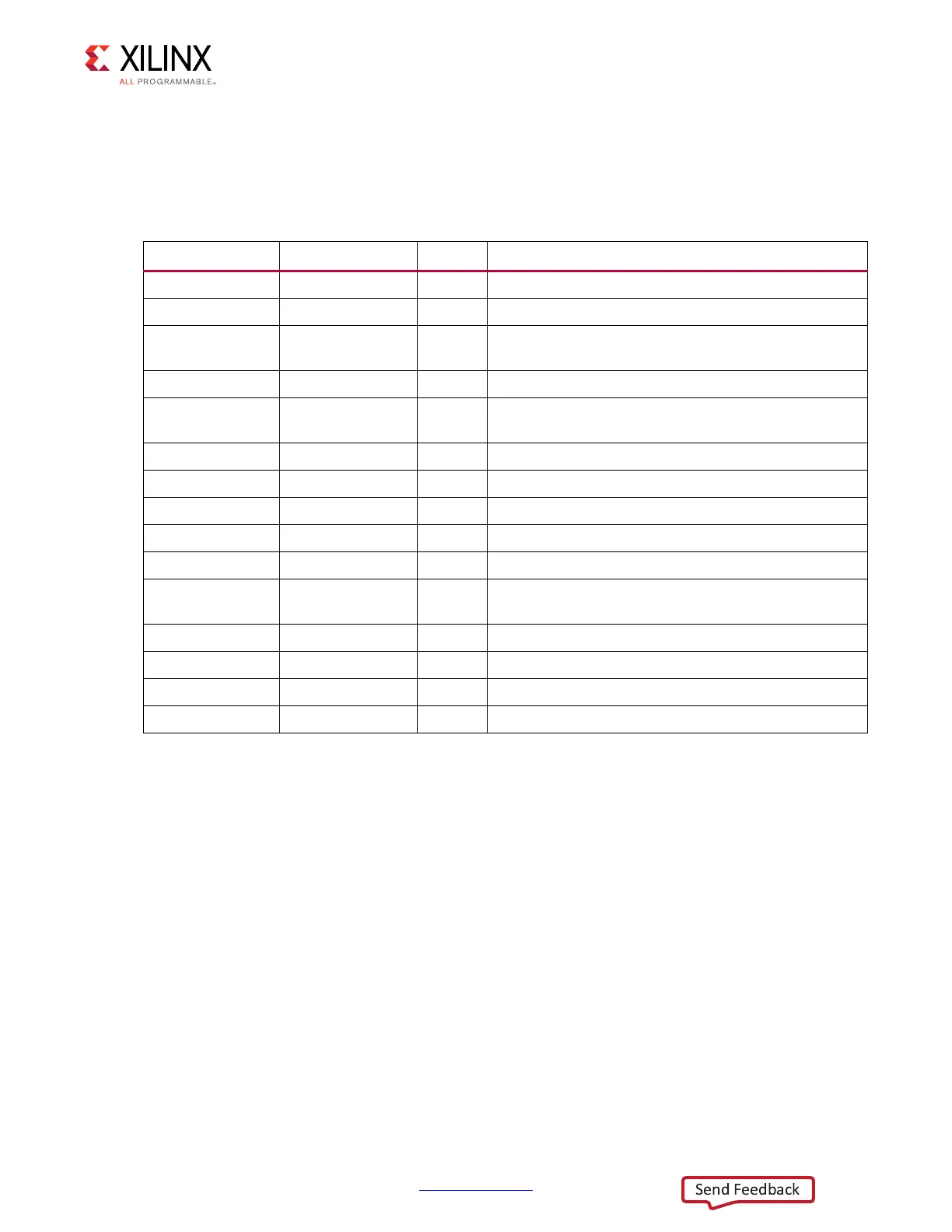

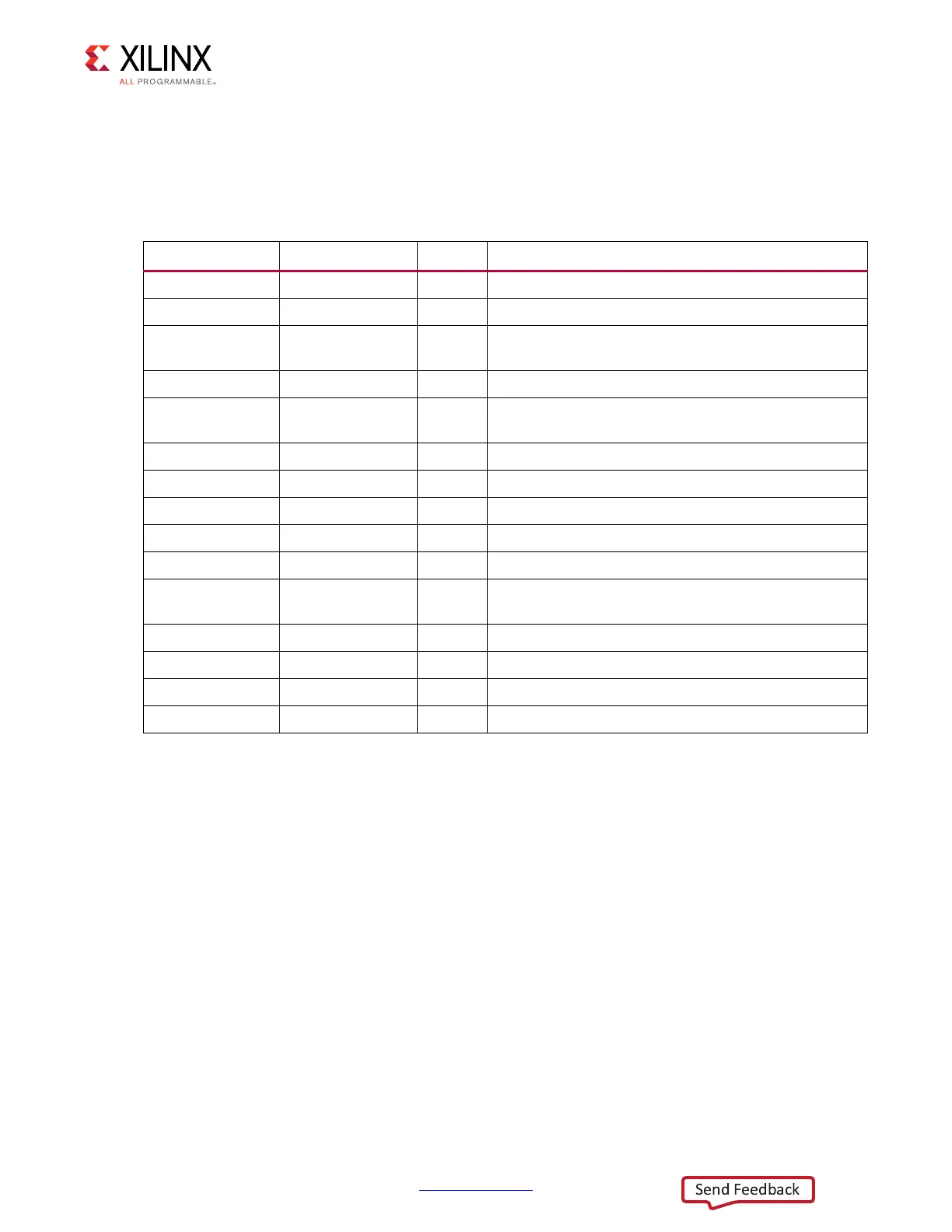

I/O Voltage Rails

There are nine PL I/O banks available on the XCZU9EG MPSoC. The voltages applied to the

XCZU9EG MPSoC I/O banks used by the ZCU102 board are listed in Table 3-2.

PS-Side: DDR4 SODIMM Socket

[Figure 2-1, callout 2]

The PS-side memory is wired to the Zynq UltraScale+ DDRC hard memory controller. A

64-bit single rank DDR4 SODIMM with ECC (72-bit) is inserted into socket J1. The ZCU102

is shipped with a DDR4 SODIMM installed:

• Manufacturer: Kingston

• Part Number: KVR21SE15S8/4

•Description:

°

4GByte DDR4 SODIMM

°

Single Rank x8

°

512Mbit x 72-Bit

°

PC4-2133 260-Pin

Table 3-2: I/O Voltage Rails

XCZU9EG Power Net Name Voltage Connected To

PL Bank 0

NA NA

MPSoC Configuration Bank 0

PL Bank 44

V

CC3V3

3.3V

GPIO DIP SW, PB SW, LEDs, 74.25 MHz CLK

PL Bank 47

V

CC3V3

3.3V

GPIO PMOD0 (RT-ANG. FEMALE), PMOD1 (STR.

MALE), PL I2C1, TRACEDATA, 125 MHz CLK

PL Bank 48

V

CC3V3

3.3V

TRACEDATA

PL Bank 49

V

CC3V3

3.3V

HDMI Codec, SYSMON I2C, SFP CTRL, UART2, MSP430

UCA1

PL Bank 50

V

CC3V3

3.3V

HDMI Codec, MSP430 GPIO, PL I2C0, PROTO. HDR. IO

PL Bank 64

V

CC1V2

1.2V

DDR4 DQ[0:15], DDR4 ADDR/CTRL, USER_SI570 CLK

PL Bank 65

V

ADJ_FMC

(1)

1.8V

FMC_HPC1 LA BUS, HDMI TX

PL Bank 66

V

ADJ_FMC

(1)

1.8V

FMC_HPC0 LA BUS, HDMI REC CLK

PL Bank 67

V

ADJ_FMC

(1)

1.8V

FMC_HPC0 LA BUS, SFP REC CLK

PS Bank 500

V

CCOPS

1.8V

QSPI LWR, QSPI UPR, UART1, MIO_I2C0, MIO_I2C1,

MIO_RXD/TXD, CAN IF

PS Bank 501

V

CCOPS

1.8V

MIO_SD IF, MIO_PMU IF, MIO_DP IF

PS Bank 502

V

CCOPS

1.8V

MIO_ENET, MIO_USB

PS Bank 503

V

CCOPS3

1.81V

PS CONFIGURATION IF

PS DDR Bank 504

V

CCO_PSDDR_504

1.2V

DDR4 SODIMM IF

Notes:

1. The ZCU102 board is shipped with V

ADJ_FMC

set to 1.8V by the MSP430 system controller.

Loading...

Loading...