ZCU102 Evaluation Board User Guide www.xilinx.com 60

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

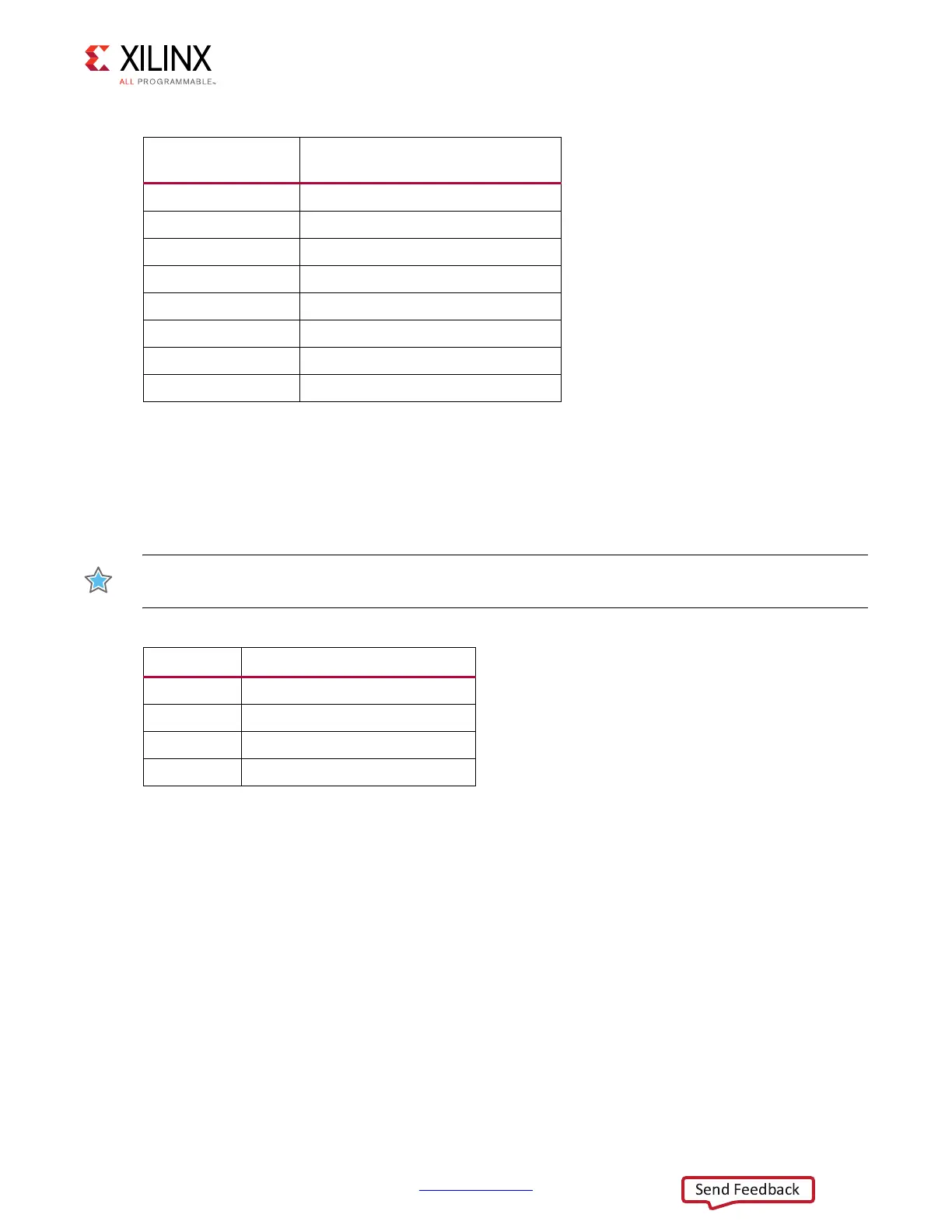

UART0 (MIO 18-19)

This is the primary Zynq UltraScale+ MPSoC PS-side UART interface and is connected to the

U40 CP2108 USB-to-Quad-UART bridge with port assignments as listed in Table 3-25.

PS-side UART0 is accessed through the U40 CP2108 USB-to-Quad-UART bridge port 0.

IMPORTANT: Use SiLabs CP210X VCP driver version 6.7.0 or later for proper USB enumeration as

identified in Table 3-25.

UART1 (MIO 20-21)

PS-side UART1 is accessed through the U40 CP2108 USB-to-Quad-UART Bridge port 1. The

CP2108 Channel 1 PS-side UART interface circuit is shown in Figure 3-19. The connections

from XCZU9EG U1 to CP2108 U40 via L/S U54 are listed in Table 3-26.

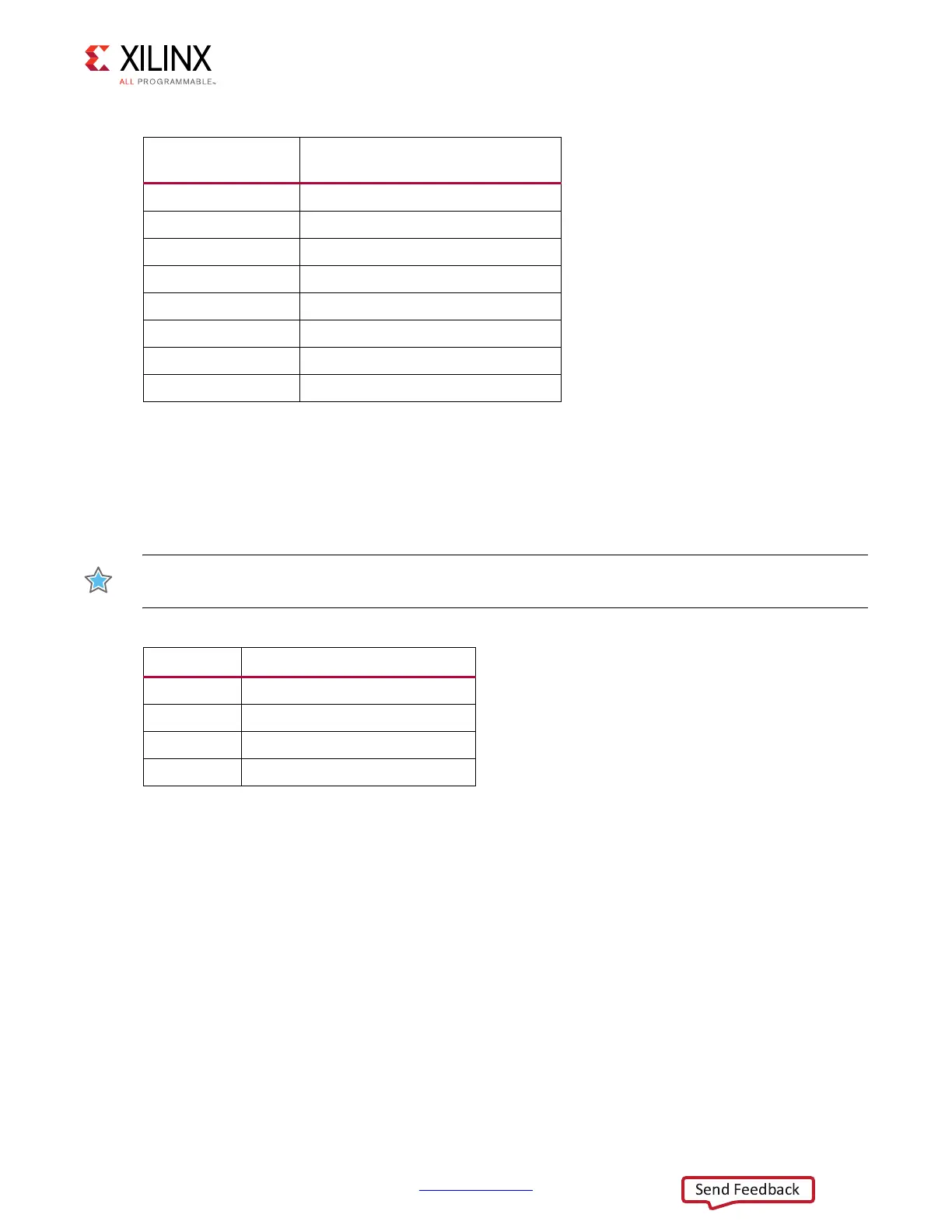

Table 3-24: I2C1 TCA9548A U135 Multiplexer Connections

U135 I2C Mux

(Addr 0x75) Port

I2C BUS 1 Device(s)

0

FMC HPC_0

1

FMC HPC_1

2

SYSMON

3

DDR4 SODIMM

4

SFP_3

5

SFP_2

6

SFP_1

7

SFP_0

Table 3-25: CP2108 UART Assignments

CP2108 U40 Zynq UltraScale+ MPSoC

UART0

PS_UART0 (MIO 18-19)

UART1

PS_UART1 (MIO 20-21)

UART2

PL-UART (HD Bank 49)

UART3

U41 System Controller UART

Loading...

Loading...