ZCU102 Evaluation Board User Guide www.xilinx.com 2

UG1182 (v1.2) March 20, 2017

Revision History

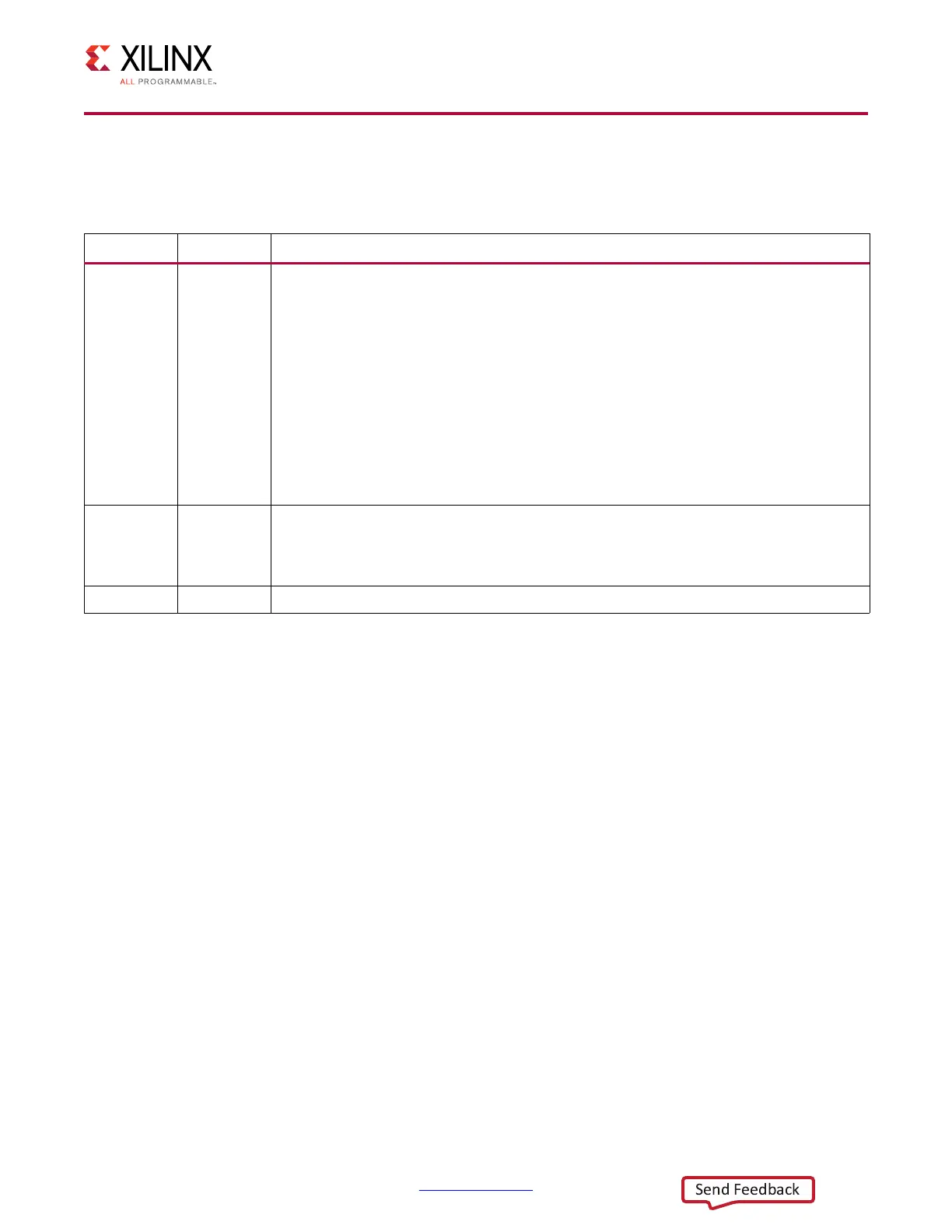

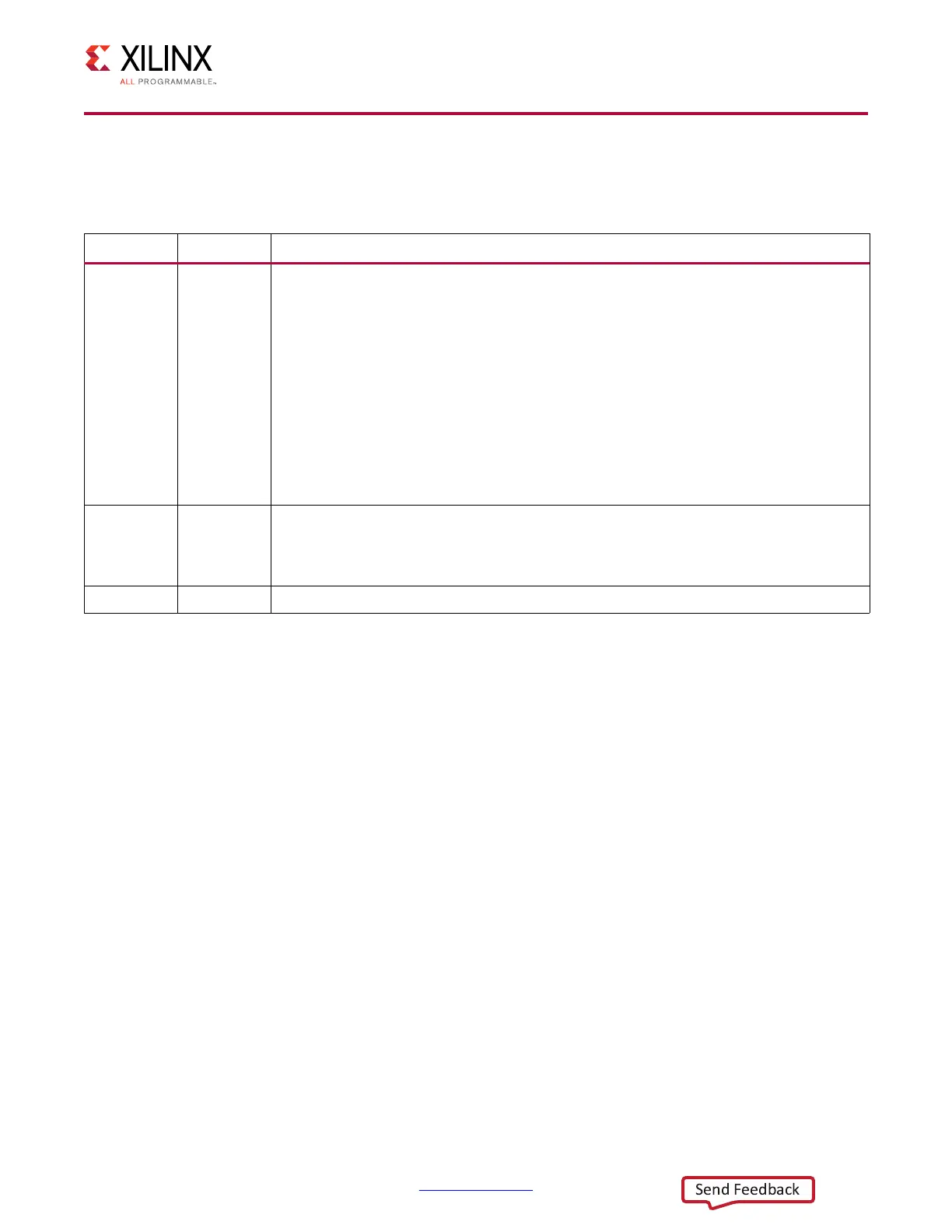

The following table shows the revision history for this document.

Date Version Revision

03/20/2017 1.2

Added notes to Dimensions in Chapter 1. Updated SW6 default switch setting in

Table 2-2 and SD configuration setting in Table 2-4. Clarified SW6[4:1] boot mode pin

settings under Quad-SPI and SD in Chapter 2. Changed “DDR SODIMM Memory J1”

heading to “DDR Component Memory” in Table 3-4. Changed PS_REF_CLK frequency

from 33 MHz to 33.33 MHz in Table 3-12. Changed “UART2_RTS_O_B” to

“UART2_CTS_O_B” in Table 3-16. Replaced Figure 3-16. Changed “QSPI119 (LWR),

U120 (UPR)” heading to “MSP430 U41” in Table 3-17. Clarified references to

Figure 3-17 in Table 3-19 and Table 3-20. Added addresses to titles in Table 3-21 and

Table 3-22 and headings in Table 3-23 and Table 3-24. Changed “22” to “L22” in

Table 3-28. Updated GTH connectivity for Quad 128, Quad 228, Quad 229, and

Quad 23 under GTH Transceivers in Chapter 3. Updated bank assignments in

Figure 3-35. Added callout 44 to Switches in Chapter 3. Updated Xilinx websites in

Appendix D, Additional Resources and Legal Notices.

11/16/2016 1.1

Updated device part number from XCZU9EG-2FFVB1156 to XCZU9EG-2FFVB1156I

throughout document. Updated board photos (Figure 2-1 and Figure 2-1) to rev 1.0.

Updated Table 2-1 and Table 2-3. Updated Chapter 3, Component Descriptions.

Updated Appendix B, Master Constraints File Listing.

05/11/2016 1.0

Initial Xilinx release - limited distribution.

Loading...

Loading...