ZCU102 Evaluation Board User Guide www.xilinx.com 41

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

FMC Connector JTAG Bypass

When an FPGA mezzanine card (FMC) is attached to J5 or J4 it is automatically added to the

JTAG chain through electronically controlled single-pole single-throw (SPST) switches U27

and U24. The SPST switches are normally closed and transition to an open state when an

FMC is attached. Switch U27 adds an attached FMC to the JTAG chain as determined by the

FMC_HPC0_PRSNT_M2C_B signal. Switch U24 adds an attached FMC to the JTAG chain as

determined by the FMC_HPC1_PRSNT_M2C_B signal. The attached FMC card must

implement a TDI-to-TDO connection using a device or bypass jumper to ensure that the

JTAG chain connects to the XCZU9EG MPSoC.

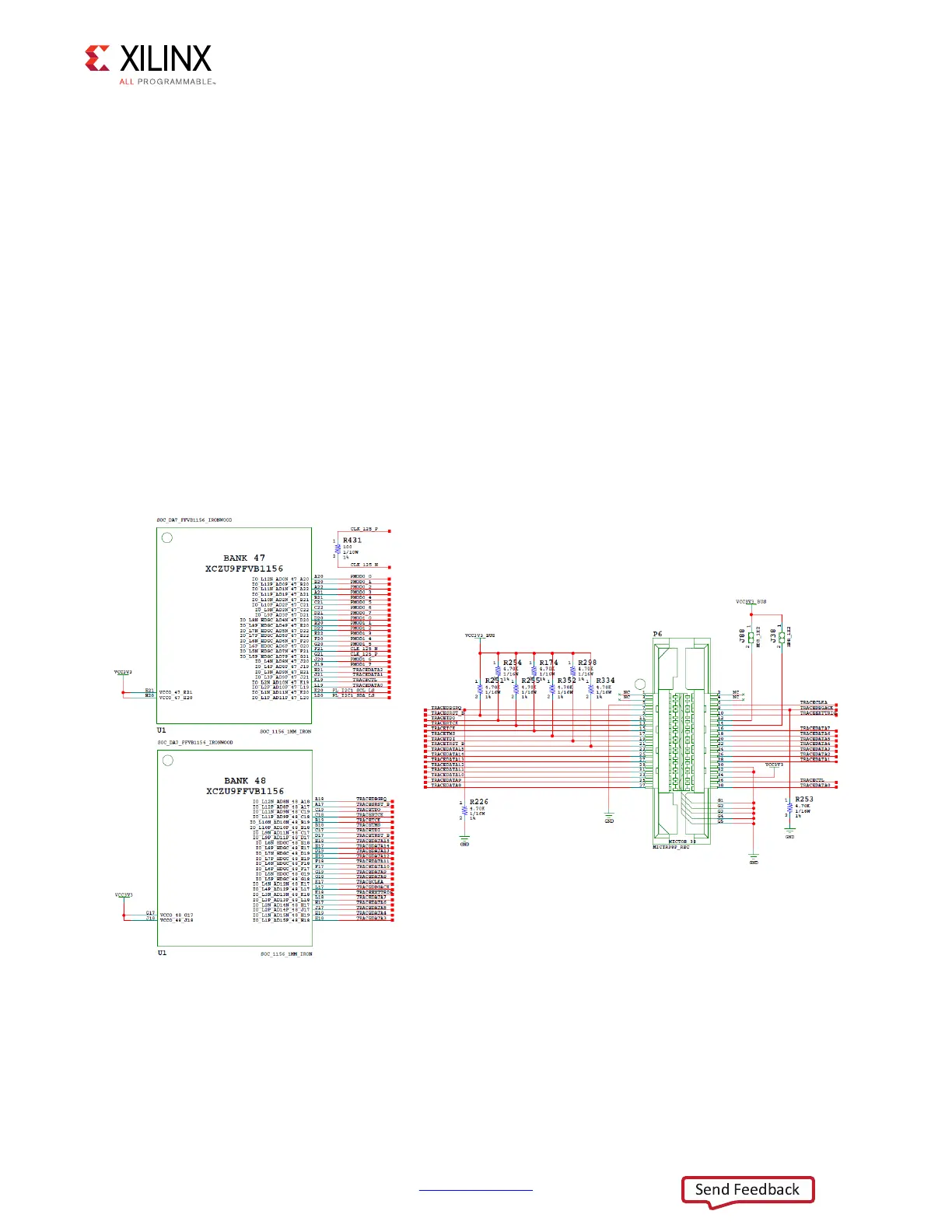

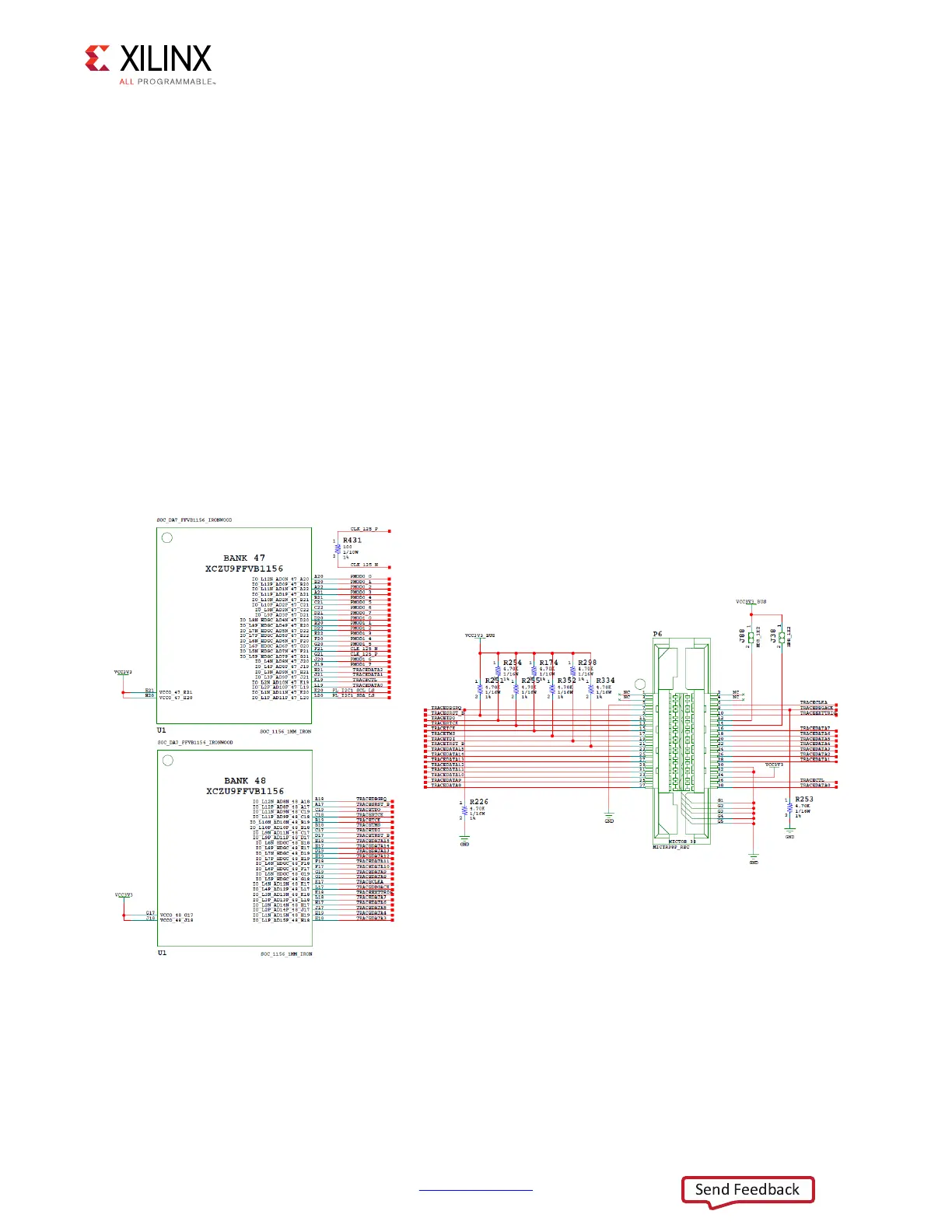

EMIO ARM Trace Port

[Figure 2-1, callout 43]

The ZCU102 evaluation board provides a trace/debug 38-pin Mictor connector, P6.

Figure 3-7 shows connector P6 with its MPSoC Bank 47/48 connections.

X-Ref Target - Figure 3-7

Figure 3-7: EMIO ARM Trace Port Interface

Loading...

Loading...