ZCU102 Evaluation Board User Guide www.xilinx.com 53

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

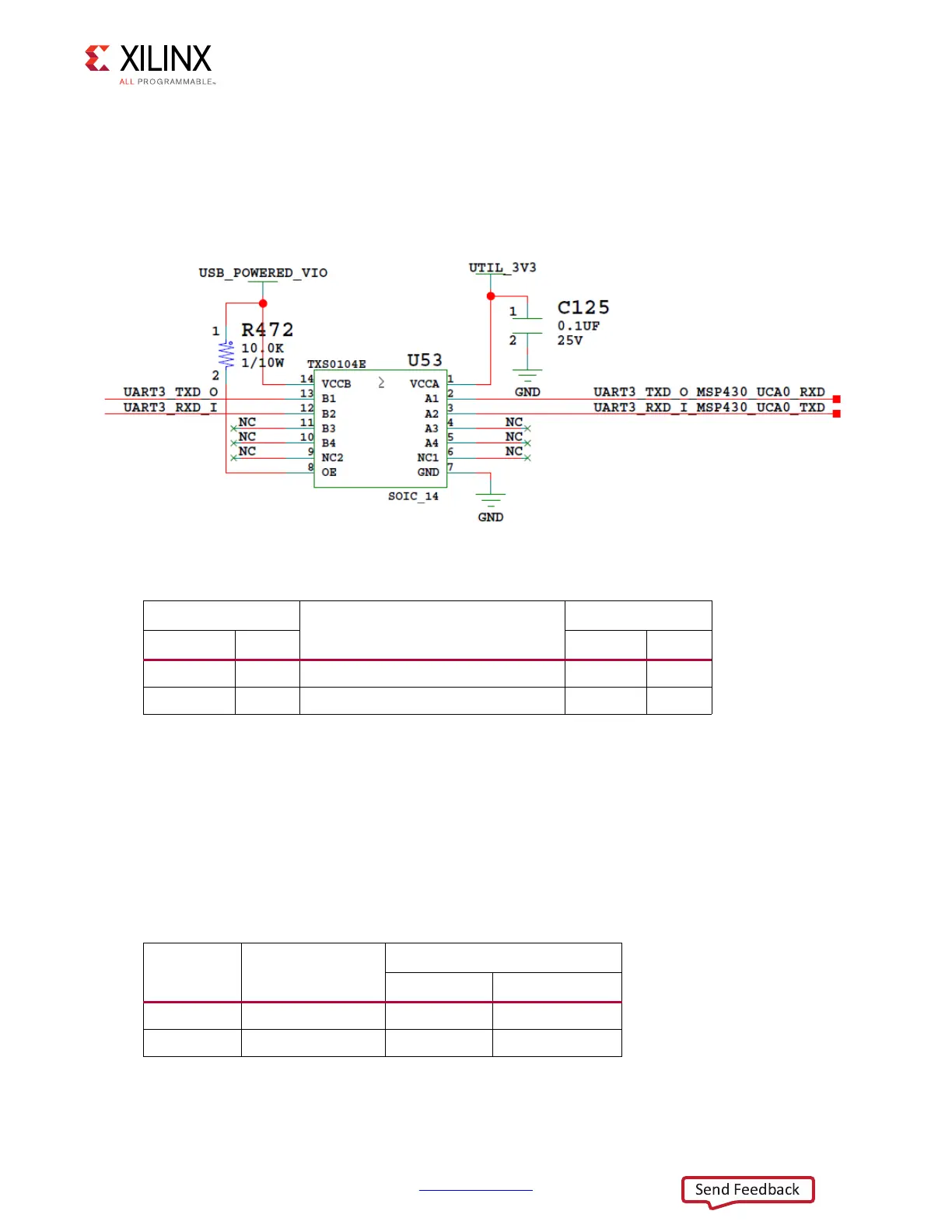

CP2108 Channel 3 MSP430 UART Interface

The CP2108 Channel 3 MSP430 UART interface circuit is shown in Figure 3-16. The

connections from MSP430 U41 to CP2108 U40 via TSX0104E level shifter U53 are listed in

Table 3-17.

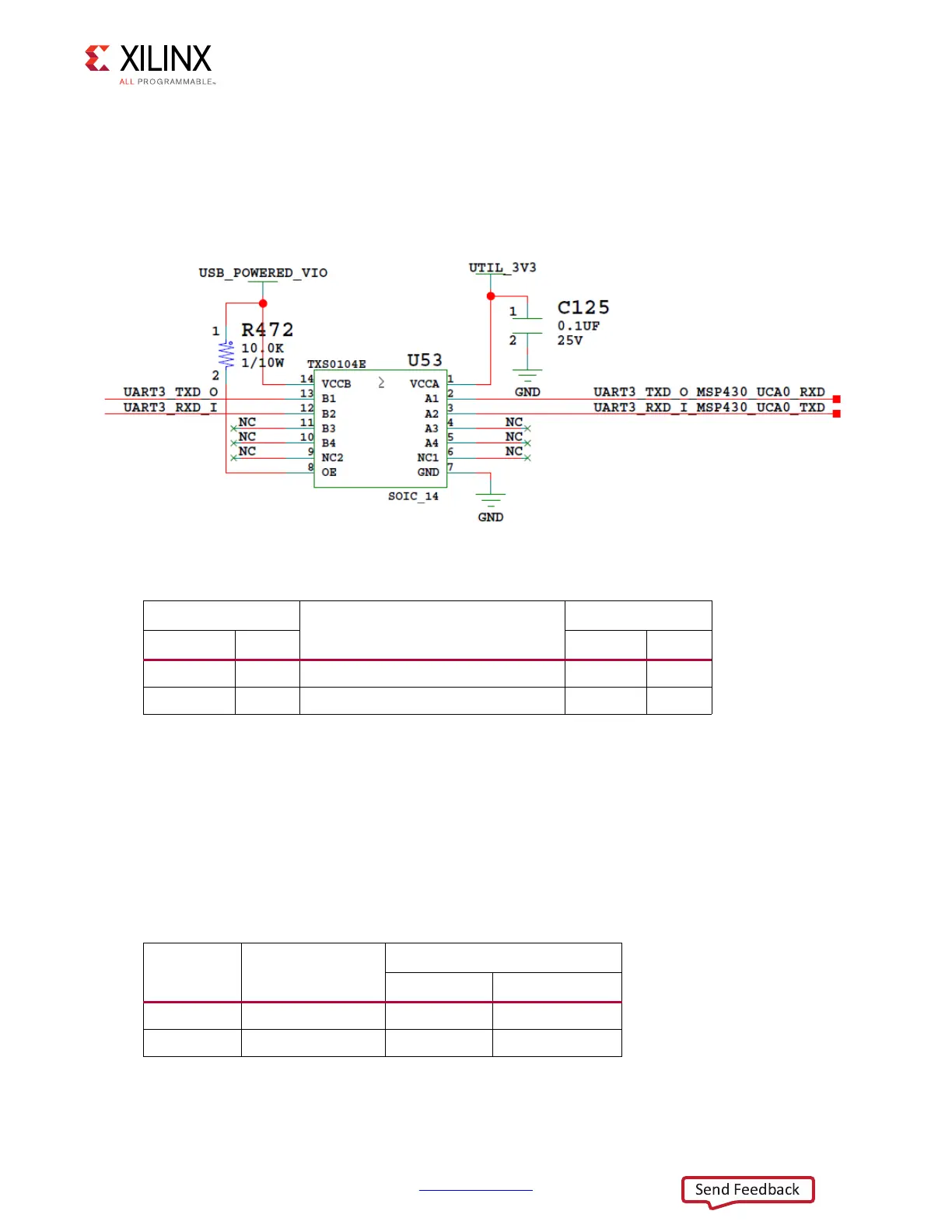

GPIO (MIO 13, 38)

These two (2) GPIO bits are connected to the U41 MSP430 system controller for general

purpose signaling or communications between the Zynq UltraScale+ MPSoC device and the

MSP430 system controller. These signals are level-shifted by TSX0108E U141. The

connections between the U41 system controller and the XCZU9EG MPSoC are listed in

Table 3-18.

X-Ref Target - Figure 3-16

Figure 3-16: MSP430 USB UART Interface

Table 3-17: MSP430 U41 to CP2108 U40 Connections via L/S U53

MSP430 U41

Schematic Net Name

CP2108 U40

Pin Name Pin No. Pin Name Pin No.

P3_3 26

UART3_TXD_O_MSP430_UCA0_RXD

TX_3 4

P3_3 25

UART3_RXD_I_MSP430_UCA0_TXD

RX_3 1

Table 3-18: System Controller U41 GPIO Connections to XCZU9EG U1

XCZU9EG

(U1) Pin

Net Name

MSP430 U41

Pin Name Pin No.

AK17

MIO13_PS_GPIO2

20 P1_7

L23

MIO38_PS_GPIO1

19 P1_6

Loading...

Loading...