ZCU102 Evaluation Board User Guide www.xilinx.com 32

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

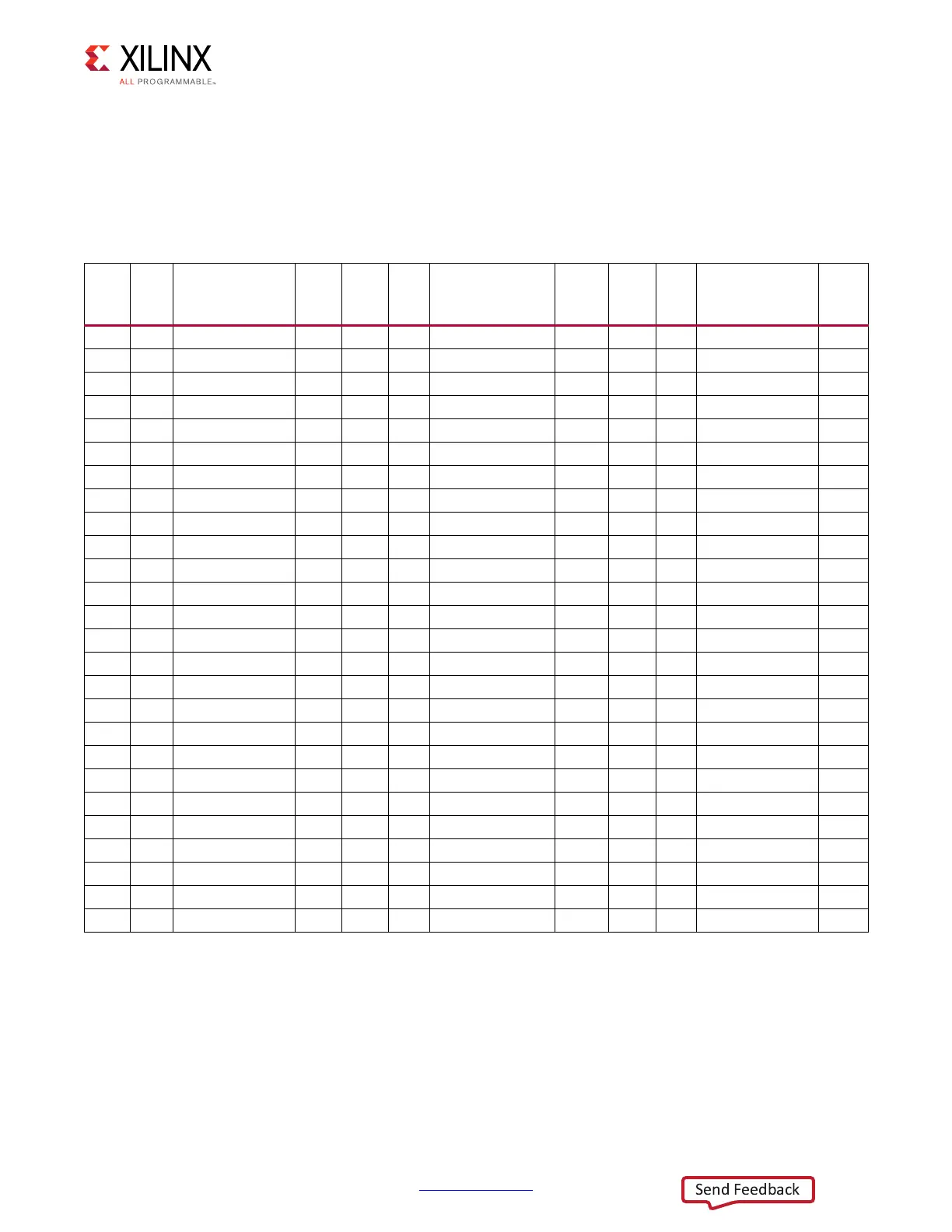

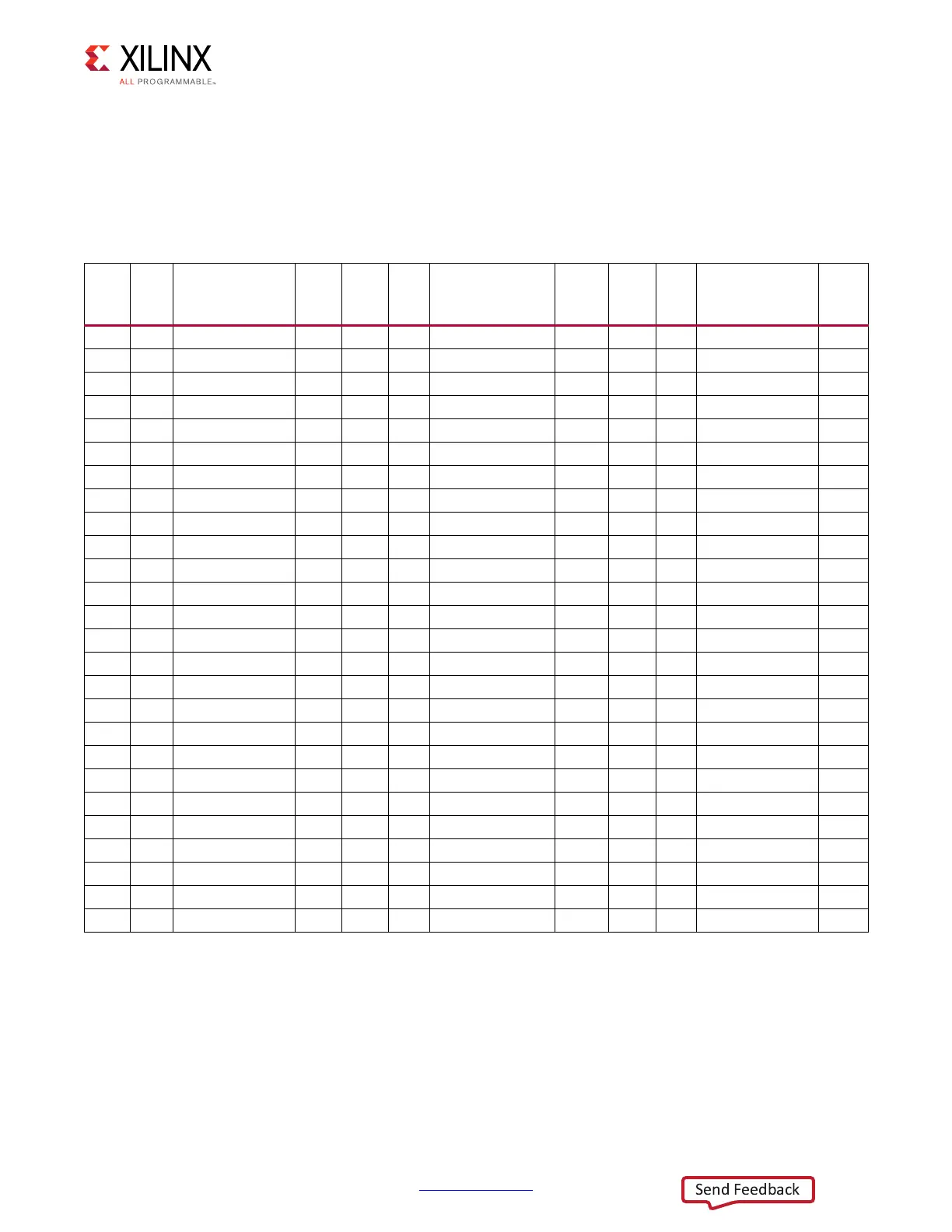

PSMIO

Table 3-5 provides PS MIO peripheral mapping implemented on the ZCU102 board. See the

Zynq UltraScale+ MPSoC Technical Reference Manual (UG1085) [Ref 2] for more information

on PS MIO peripheral mapping.

Table 3-5: ZCU102 MIO Connections

MIO

[25:0]

Bank

500

ZU7EV

U1 Pin

No.

Schematic Net Name Type

MIO

[51:26]

Bank

501

ZU7EV

U1 Pin

No.

Schematic Net Name Type

MIO

[77:52]

Bank

502

ZU7EV

U1 Pin

No.

Schematic Net Name Type

MIO25 AE19 MIO25_CAN_RX CAN1 MIO51 N25 MIO51_SDIO_CLK_R SD1 MIO77 F25 MIO77_ENET_MDIO

MDIO3

MIO24 AE20 MIO24_CAN_TX CAN1 MIO50 P25 MIO50_SDIO_CMD_R SD1 MIO76 H25 MIO76_ENET_MDC

MDIO3

MIO23 AD19 MIO23_LED GPIO MIO49 K25 MIO49_SDIO_DAT3_R SD1 MIO75 D25 MIO75_ENET_RX_CTRL

GEM3

MIO22 AD20 MIO22_BUTTON GPIO MIO48 M25 MIO48_SDIO_DAT2_R SD1 MIO74 G25 MIO74_ENET_RX_D3

GEM3

MIO21 AF18 MIO21_UART1_RXD UART1 MIO47 L25 MIO47_SDIO_DAT1_R SD1 MIO73 H24 MIO73_ENET_RX_D2

GEM3

MIO20 AD18 MIO20_UART1_TXD UART1 MIO46 J25 MIO46_SDIO_DAT0_R SD1 MIO72 E25 MIO72_ENET_RX_D1

GEM3

MIO19 AL17 MIO19_UART0_TXD UART0 MIO45 P24 MIO45_SDIO_DETECT SD1 MIO71 C27 MIO71_ENET_RX_D0

GEM3

MIO18 AE18 MIO18_UART0_RXD UART0 MIO44 N24 MIO44_SDIO_PROTECT SD1 MIO70 C26 MIO70_ENET_RX_CLK

GEM3

MIO17 AP16 MIO17_I2C1_SDA I2C1 MIO43 K24 Not Connected NC MIO69 B27 MIO69_ENET_TX_CTRL

GEM3

MIO16 AM16 MIO16_I2C1_SCL I2C1 MIO42 M24 MIO42_SDIO_DIR_DAT1 SD1 MIO68 B26 MIO68_ENET_TX_D3

GEM3

MIO15 AN16 MIO15_I2C0_SDA I2C0 MIO41 J24 MIO41_SDIO_DIR_DAT0 SD1 MIO67 B25 MIO67_ENET_TX_D2

GEM3

MIO14 AL16 MIO14_I2C0_SCL I2C0 MIO40 M23 MIO40_SDIO_DIR_CMD SD1 MIO66 A27 MIO66_ENET_TX_D1

GEM3

MIO13 AK17 MIO13 PS_GPIO2 GPIO MIO39 N23 MIO39_SDIO_SEL SD1 MIO65 A26 MIO65_ENET_TX_D0

GEM3

MIO12 AJ17 MIO12_QSPI_UPR_CLK QSP1 MIO38 L23 MIO38_PS_GPIO1 GPIO MIO64 A25 MIO64_ENET_TX_CLK

GEM3

MIO11 AF17 MIO11_QSPI_UPR_DQ3 QSP1 MIO37 N22 MIO37_PMU_GPO5 PM OUT MIO63 D24 MIO63_USB_DATA7_R

USB0

MIO10 AH17 MIO10_QSPI_UPR_DQ2 QSP1 MIO36 K23 MIO36_PMU_GPO4 PM OUT MIO62 G24 MIO62_USB_DATA6_R

USB0

MIO9 AP15 MIO9_QSPI_UPR_DQ1 QSP1 MIO35 P22 MIO35_PMU_GPO3 PM OUT MIO61 C24 MIO61_USB_DATA5_R

USB0

MIO8 AE17 MIO8_QSPI_UPR_DQ0 QSP1 MIO34 L22 MIO34_PMU_GPO2 PM OUT MIO60 E24 MIO60_USB_DATA4_R

USB0

MIO7 AD17 MIO7_QSPI_UPR_CS_B QSP1 MIO33 H23 MIO33_PMU_GPO1 PM OUT MIO59 B24 MIO59_USB_DATA3_R

USB0

MIO6 AL15 Not Connected NC MIO32 H22 MIO32_PMU_GPO0 PM OUT MIO58 G23 MIO58_USB_STP_R

USB0

MIO5 AM15 MIO5_QSPI_LWR_CS_B QSP1 MIO31 J22 MIO31_PCIE_RESET_N PCIE MIO57 A23 MIO57_USB_DATA1_R

USB0

MIO4 AH16 MIO4_QSPI_LWR_DQ0 QSP1 MIO30 L21 MIO30_DP_AUX_IN DPAUX MIO56 C23 MIO56_USB_DATA0_R

USB0

MIO3 AG16 MIO3_QSPI_LWR_DQ3 QSP1 MIO29 K22 MIO29_DP_OE DPAUX MIO55 B23 MIO55_USB_NXT

USB0

MIO2 AD16 MIO2_QSPI_LWR_DQ2 QSP1 MIO28 N21 MIO28_DP_HPD DPAUX MIO54 F23 MIO54_USB_DATA2_R

USB0

MIO1 AJ16 MIO1_QSPI_LWR_DQ1 QSP1 MIO27 M21 MIO27_DP_AUX_OUT DPAUX MIO53 E23 MIO53_USB_DIR

USB0

MIO0 AF16 MIO0_QSPI_LWR_CLK QSP1 MIO26 P21 MIO26_PMU_INPUT PMU IN MIO52 F22 MIO52_USB_CLK

USB0

Loading...

Loading...