ZCU102 Evaluation Board User Guide www.xilinx.com 98

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

FMC HPC1 Connector J4

[Figure 2-1, callout 32]

The FMC connector at J4 (HPC1) implements a subset of the full FMC HPC connectivity:

• 60 single-ended, or 30 differential user-defined pairs (LA[00:29])

• Eight GTH transceiver DP differential pairs

• Two GBTCLK differential clocks

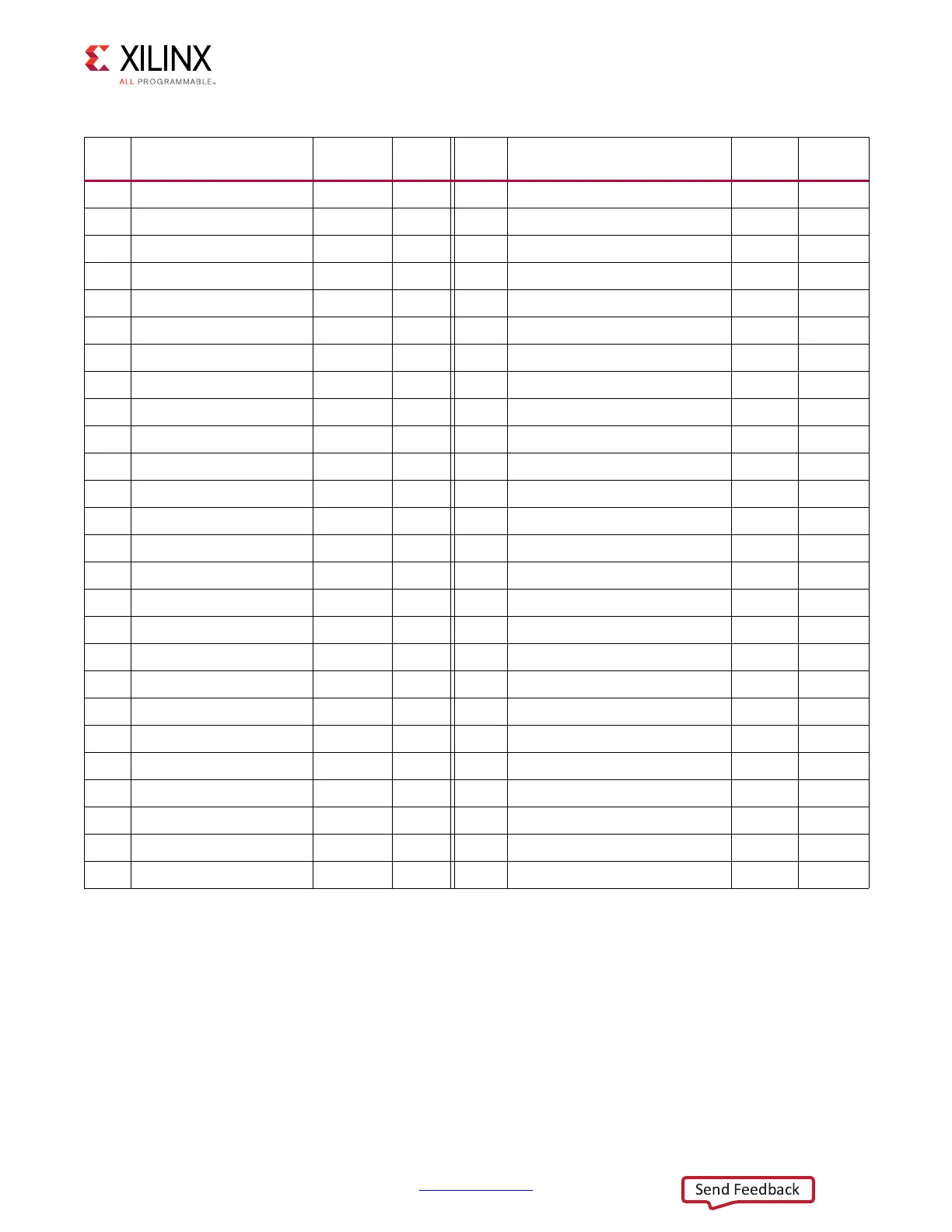

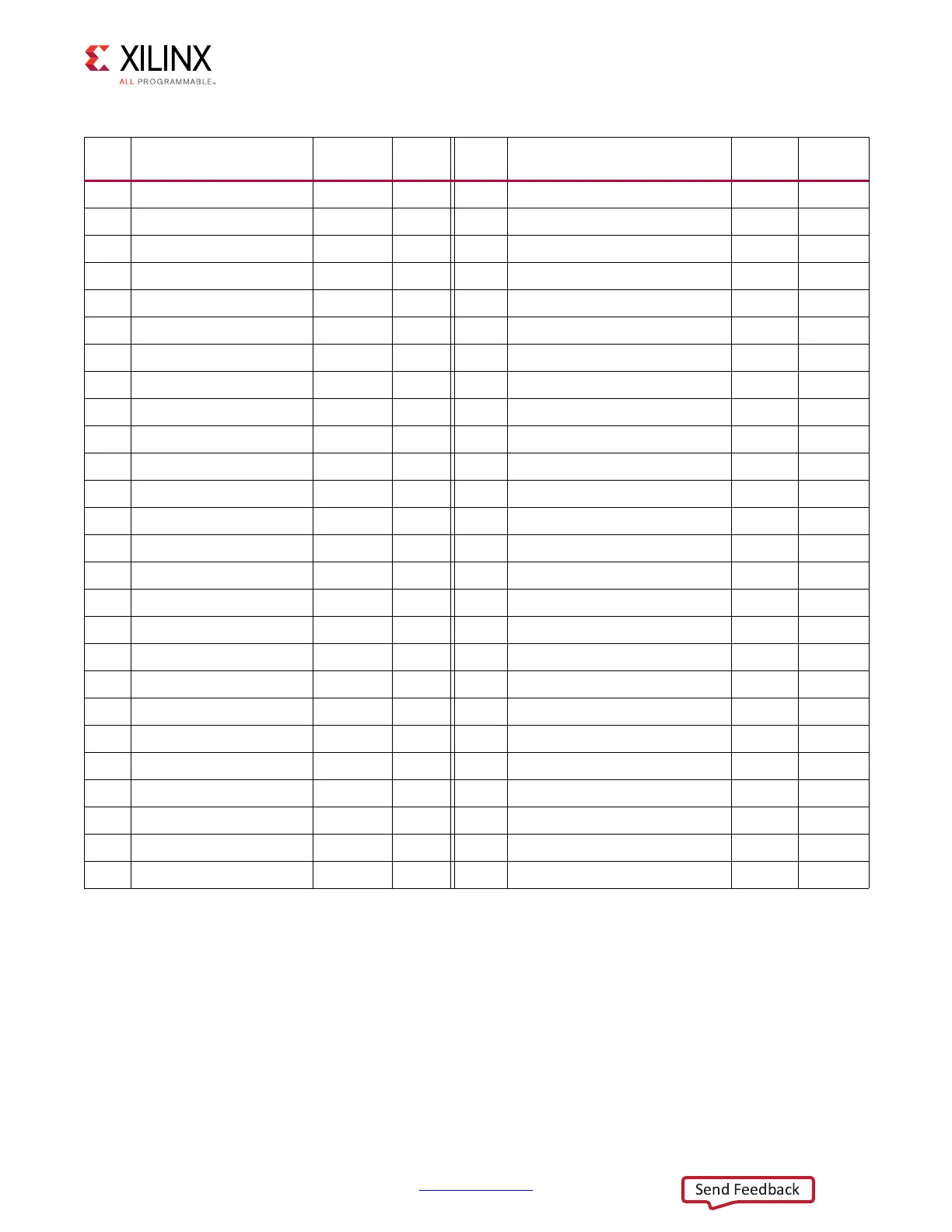

Table 3-48: J5 HPC0 FMC Section J and K Connections to XCZU9EG U1

J5 Pin Schematic Net Name

I/O

Standard

U1 Pin J5 Pin Schematic Net Name

I/O

Standard

U1 Pin

J2 NC K1 NC

J3 NC K4 NC

J6 NC K5 NC

J7 NC K7 NC

J9 NC K8 NC

J10 NC K10 NC

J12 NC K11 NC

J13 NC K13 NC

J15 NC K14 NC

J16 NC K16 NC

J18 NC K17 NC

J19 NC K19 NC

J21 NC K20 NC

J22 NC K22 NC

J24 NC K23 NC

J25 NC K25 NC

J27 NC K26 NC

J28 NC K28 NC

J30 NC K29 NC

J31 NC K31 NC

J33 NC K32 NC

J34 NC K34 NC

J36 NC K35 NC

J37 NC K37 NC

J39 NC K38 NC

K40 NC

Loading...

Loading...