ZCU102 Evaluation Board User Guide www.xilinx.com 58

UG1182 (v1.2) March 20, 2017

Chapter 3: Board Component Descriptions

I2C1 (MIO 16-17)

The PS-side I2C1 interface provides access to I2C peripherals through a set of I2C switches.

The I2C connection is shared with the PL-side and the system controller. Figure 3-18 shows

a high-level view of the I2C1 bus connectivity represented in Table 3-23 and Table 3-24.

TCA9548A U34 is set to 0x74 and TCA9548A U135 is set to 0x75.

U16

0X44

INA226 VCC3V3

U65

0X45

INA226 VADJ_FMC

U74

0X46

INA226 MGTAVCC

U75

0X47

INA226 MGTAVTT

MAXIM_PMBUS

J84 N/A

PMBUS Conn SDA Pin 3/SCL Pin 1

U47

0X13

MAX15301 VCCINT

U7

0X14

MAX15303 VCCBRAM

U6 0X15

MAX15303 VCCAUX

U10

0X16

MAX15303 VCC1V2

U9

0X17

MAX15303 VCC3V3

U63

0X18

MAX15301 VADJ_FMC

U95

0X72

MAX20751 MGTAVCC

U96

0X73

MAX20751 MGTAVTT

U46

0X0A

MAX15301 VCCPSINTFP

U4

0X0B

MAX15303 VCCPSINTLP

U18

0X1D

MAX15303 DDR4_DIMM_VDDQ

U13

0X10

MAX15303 VCCOPS

U49

0X1A

MAX15301 UTIL_3V3

U8

0X1B

MAX15301 UTIL_5V0

SYSMON

U1 N/A

U1 BANK 49 SDA Pin B14/SCL Pin C14

U135 N/A

TCA9548A Mux I2C1 Bus Port 2

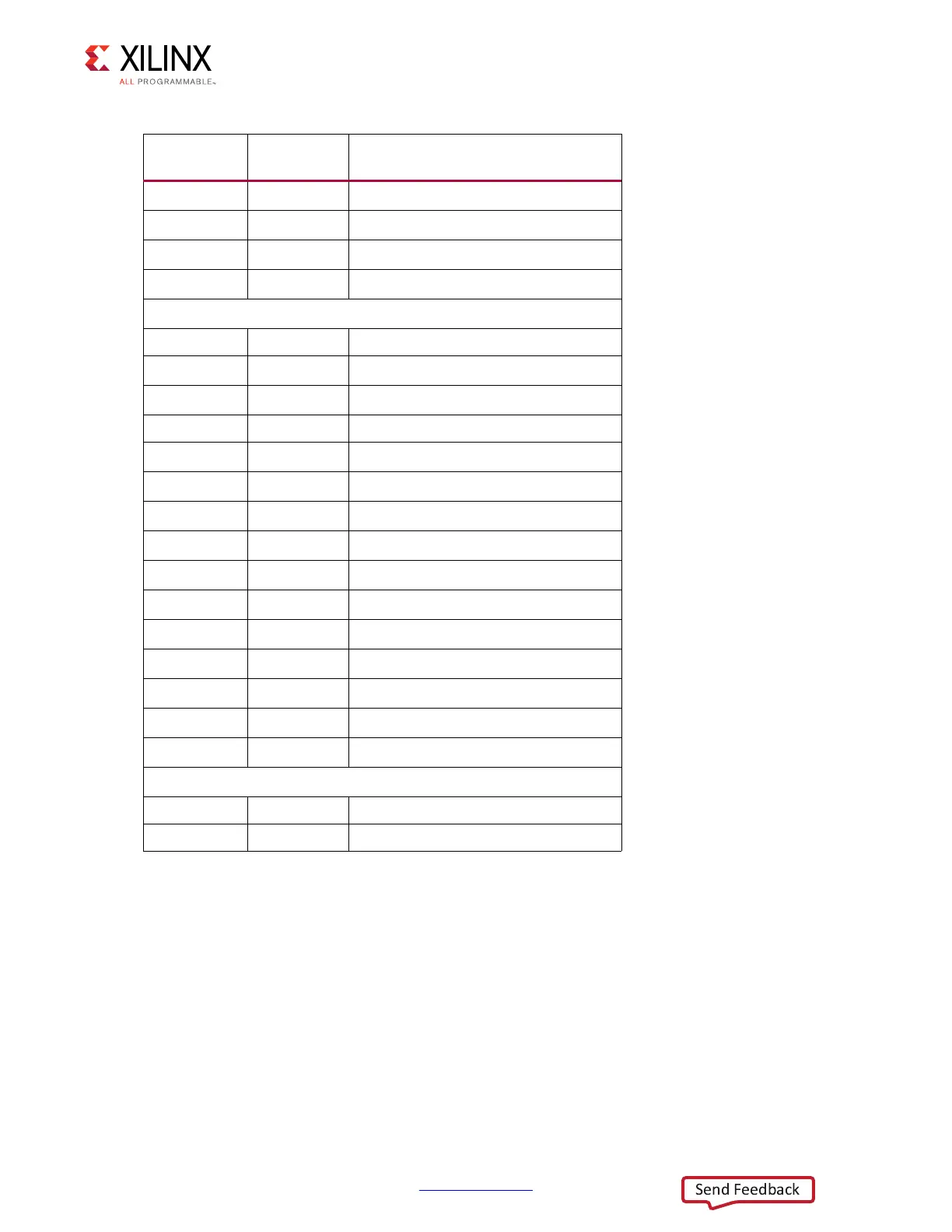

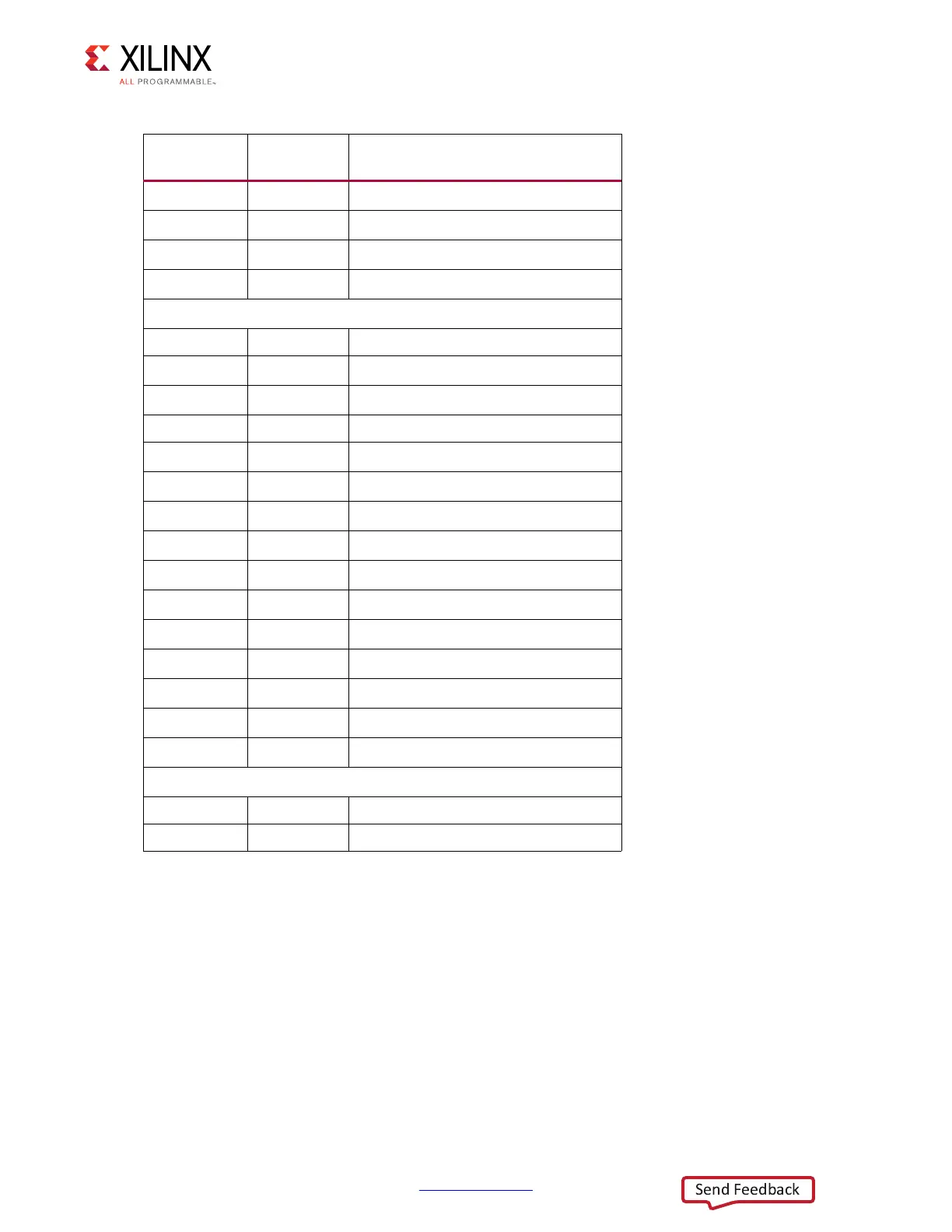

Table 3-22: I2C0 U60 (Addr. 0x75) Mux Target Bus Connections (Cont’d)

Reference

Designation

Address Device(s)

Loading...

Loading...