Publication 1747-RM001G-EN-P - November 2008

5-10 Data Handling Instructions

Updates to Arithmetic Status Bits

The arithmetic status bits are found in Word 0, bits 0 to 3 in the status file.

After an instruction is executed, the arithmetic status bits in the status file are

updated.

Decode 4 to 1 of 16 (DCD)

When executed, this instruction sets one bit of the destination word. The

particular bit that is turned on depends on the value of the first four bits of the

source word. See the table below.

Use this instruction to multiplex data in applications such as rotary switches,

keypads, and bank switching.

Table 5.5 Processor Function

With this Bit The Processor

S:0/0 Carry (C) always resets.

S:0/1 Overflow (V) sets if overflow generated or an unsupported input is detected;

otherwise resets

S:0/2 Zero (Z) sets if the result is zero; otherwise resets

S:0/3 Sign (S) sets if the result is negative; otherwise resets

DCD

Decode 4 to 1 of 16

Source N7:62

0003h<

Dest N7:63

0000000000000100<

DCD

Output Instruction

Fixed SLC

5/01

SLC

5/02

SLC

5/03

SLC

5/04

SLC

5/05

• •••••

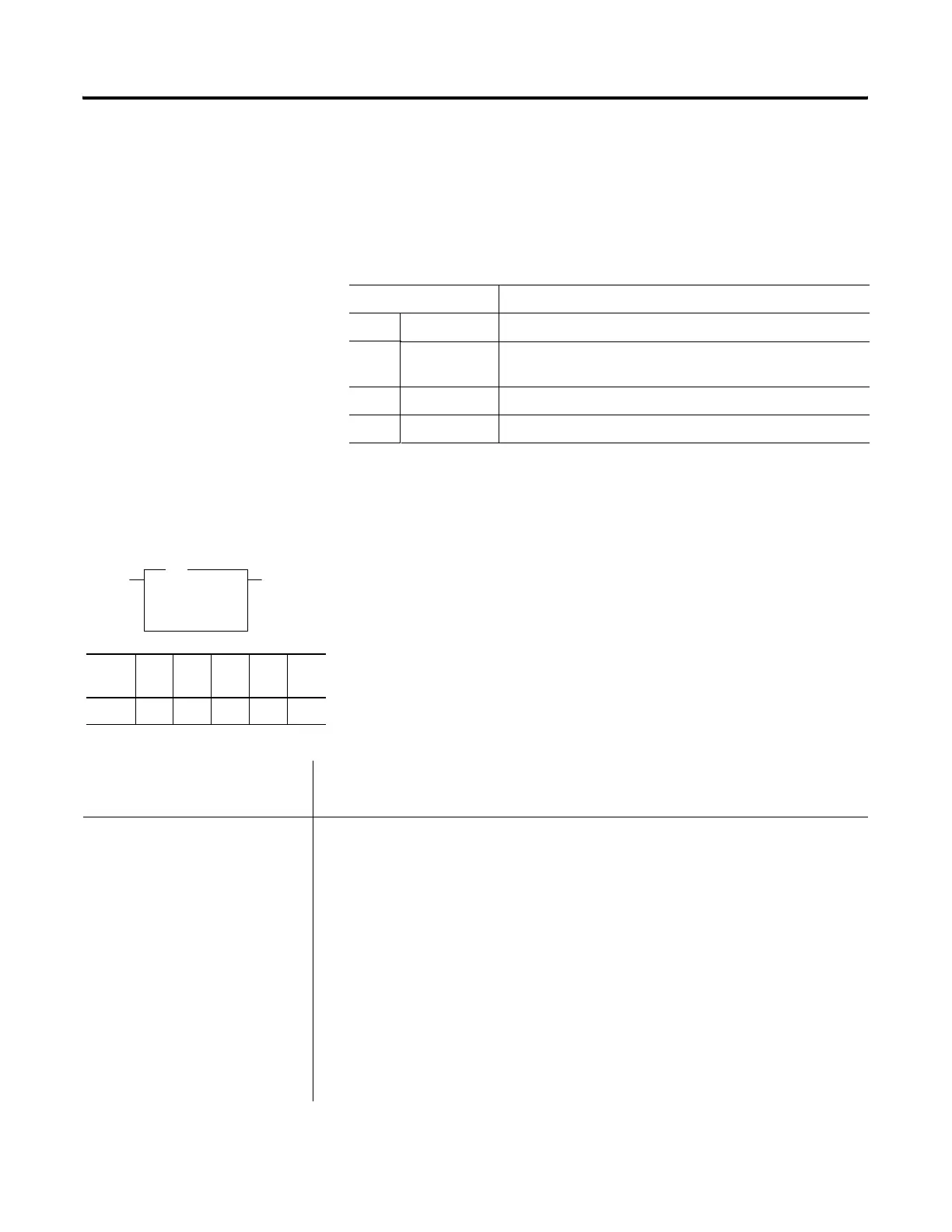

Source Destination

Bit 15-04 03 02 01 00 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Loading...

Loading...