Publication 1747-RM001G-EN-P - November 2008

2-18 Basic Instructions

The HSC differs from the CTU and CTD counters. The CTU and CTD are

software counters. The HSC is a hardware counter and operates

asynchronously to the ladder program scan. The HSC accumulated value

(C5:0.ACC) is normally updated each time the HSC rung is evaluated in the

ladder program. This means that the HSC hardware accumulator value is

transferred to the HSC software accumulator. Only use the OTE instruction

to transfer this value. The HSC instruction immediately clears bit C5:0/UA

following the accumulated update.

Many HSC counts may occur between HSC evaluations, which would make

C5:0.ACC inaccurate when used throughout a ladder program. To allow for an

accurate HSC accumulated value, the update accumulator bit (C5:0/UA)

causes C5:0.ACC to be immediately updated to the state of the hardware

accumulator when set.

Use the RES instruction to reset the high-speed counter at address C5:0. The

HSC instruction clears the status bits, the accumulator, and loads the preset

value during:

• power up.

• entry into the REM Run mode.

• a reset.

Application Example

In the following figures, rungs 1, 18, and 31 of the main program file each

consist of an XIC instruction addressed to the HSC done bit and a JSR

instruction. These rungs poll the status of the HSC done bit. When the Done

bit is set at any of these poll points, program execution moves to subroutine

file 3, executing the HSC logic. After the HSC logic is executed, the Done bit

is reset by an unlatch instruction, and program execution returns to the main

program file.

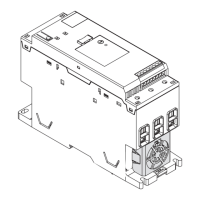

Loading...

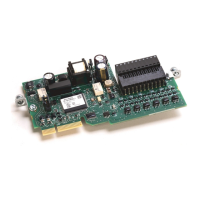

Loading...