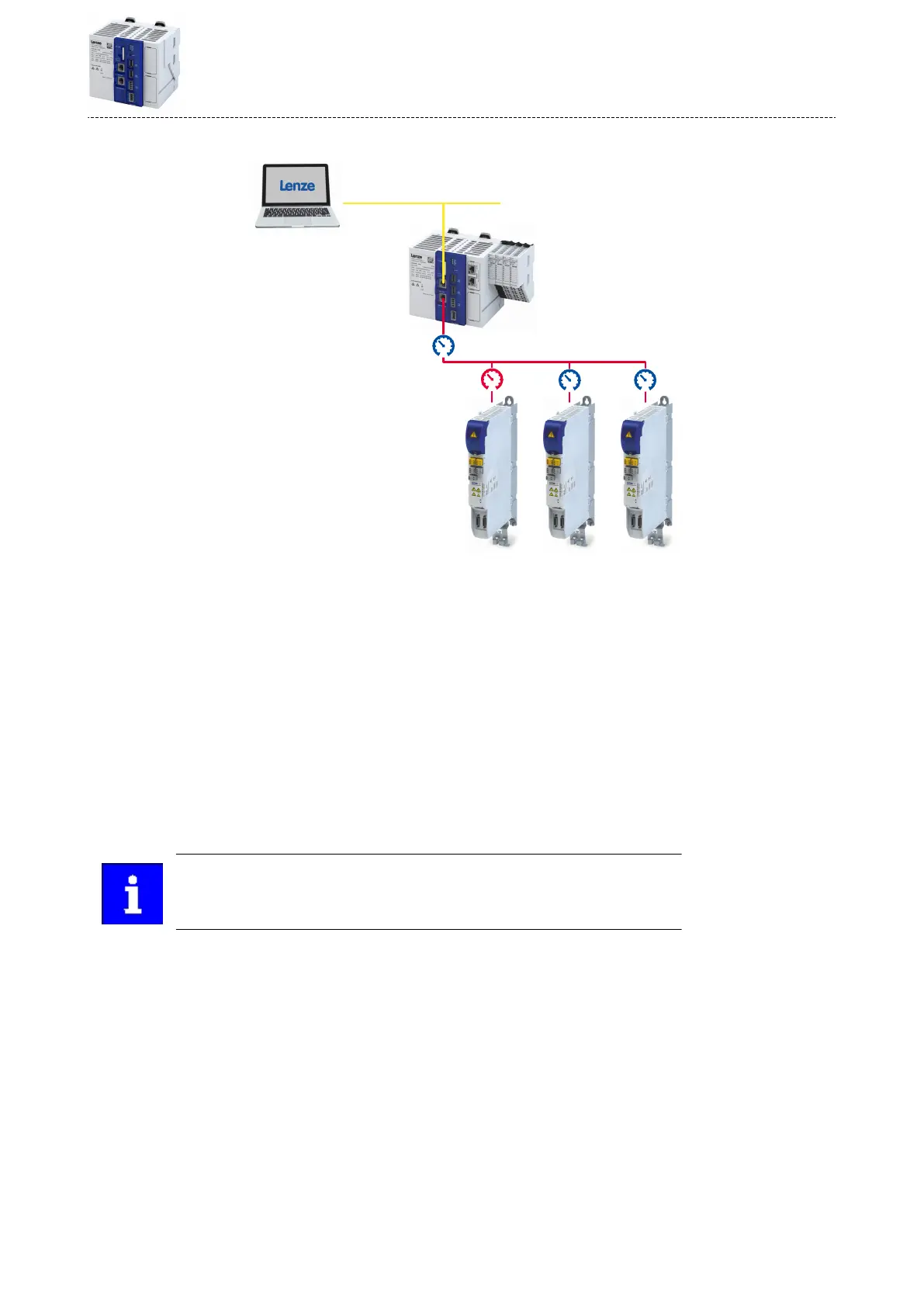

8.1.10.2 Synchronisaon with "distributed clocks" (DC)

Ethernet

Engineering PC

EtherCAT

Fig. 2: EtherCAT bus system with c520 controller and i700 servo inverter

The DC synchronizaon is set using the »PLC Designer«.

The Distributed Clocks (DC) funconality enables an exact me leveling for applicaons, in

which several axes execute simultaneous, coordinated movements. The data is accepted

synchronously with the PLC program. For DC synchronizaon, all slaves are synchronized with

a reference clock, the so-called "DC master".

Synchronous communicaon

The DC synchronizaon provides for a phase-synchronous operaon of master and slaves:

Within one bus cycle, the setpoints are accepted and the actual values are detected in the

eld devices at always exactly the same me. If the Lenze controller (master) is synchronous

with the distributed clocks, the actual values acquired by the slave are sent to the master at

the end of the bus cycle and setpoints from the master are sent to the slaves for processing.

When the next DC synchronizaon event occurs, the data is accepted.

The DC synchronizaon is only carried out in the Operaonal state.

Aer an Out-of-sync occurrence, the EtherCAT master synchronizes the slaves.

Successful synchronizaon is indicated by means of the In-Sync message.

Test of DC synchronicity

DC synchronicity is only available in the Operaonal state.

DC synchronicity check in the »PLC Designer«

•

EtherCAT master: In the Diagnosc master tab, DC In-Sync is set to TRUE if the DC master

and all DC slaves have been synchronized.

•

L_ETC_GetMasterDiagnosc funcon block (FB)/visualizaon of the

L_ETC_GetMasterDiagnosc funcon block

DC In-Sync is set to TRUE at the oDiagnosc.xDC_InSync output if the DC master and all

DC slaves are synchronized.

•

L_IODrvEtherCAT funcon block (FB) DC In-Sync is set to TRUE at the

xDistributedClockInSync output if all DC slaves are synchronized.

Conguring the network

EtherCAT

Advanced conguraon

59

Loading...

Loading...