On-Chip Cache Memories

MOTOROLA

MC68030 USER’S MANUAL

6-13

burst operation is available to the EU after the first cycle is complete. The microsequencer

must wait for the burst operation to complete before requesting the second portion of the

operand. Normally, the request for the second portion results in a data cache hit unless the

second cycle of the burst operation terminates abnormally.

The bursting mechanism allows addresses to wrap around so that the entire four long words

in the cache line can be filled in a single burst operation, regardless of the initial address and

operand alignment. Depending on the structure of the external memory system, address bits

A2 and A3 may have to be incremented externally to select the long words in the proper

order for loading into the cache. The MC68030 holds the entire address bus constant for the

duration of the burst cycle. Figure 6-12 shows an example of this address wraparound. The

initial cycle is a long-word access from address $6. Because the responding device returns

CBACK

and STERM (signaling a 32-bit port), the entire long word at base address $04 is

transferred. Since the initial address is $06 when CBREQ is asserted, the next entry to be

burst filled into the cache should correspond to address $08, then $0C, and last, $00. This

addressing is compatible with existing nibble-mode dynamic RAMs, and can be supported

by page and static column modes with an external modulo 4 counter for A2 and A3.

The MC68030 does not assert CBREQ

during the first portion of a misaligned access if the

remainder of the access does not correspond to the same cache line. Figure 6-13 shows an

example in which the first portion of a misaligned access is at address $0F. With a 32-bit

port, the first access corresponds to the cache entry at address $0C, which is filled using a

single-entry load operation. The second access, at address $10 corresponding to the

second cache line, requests a burst fill and the processor asserts CBREQ

. During this burst

operation, long words $10, $14, $18, and $1C are all filled in that order.

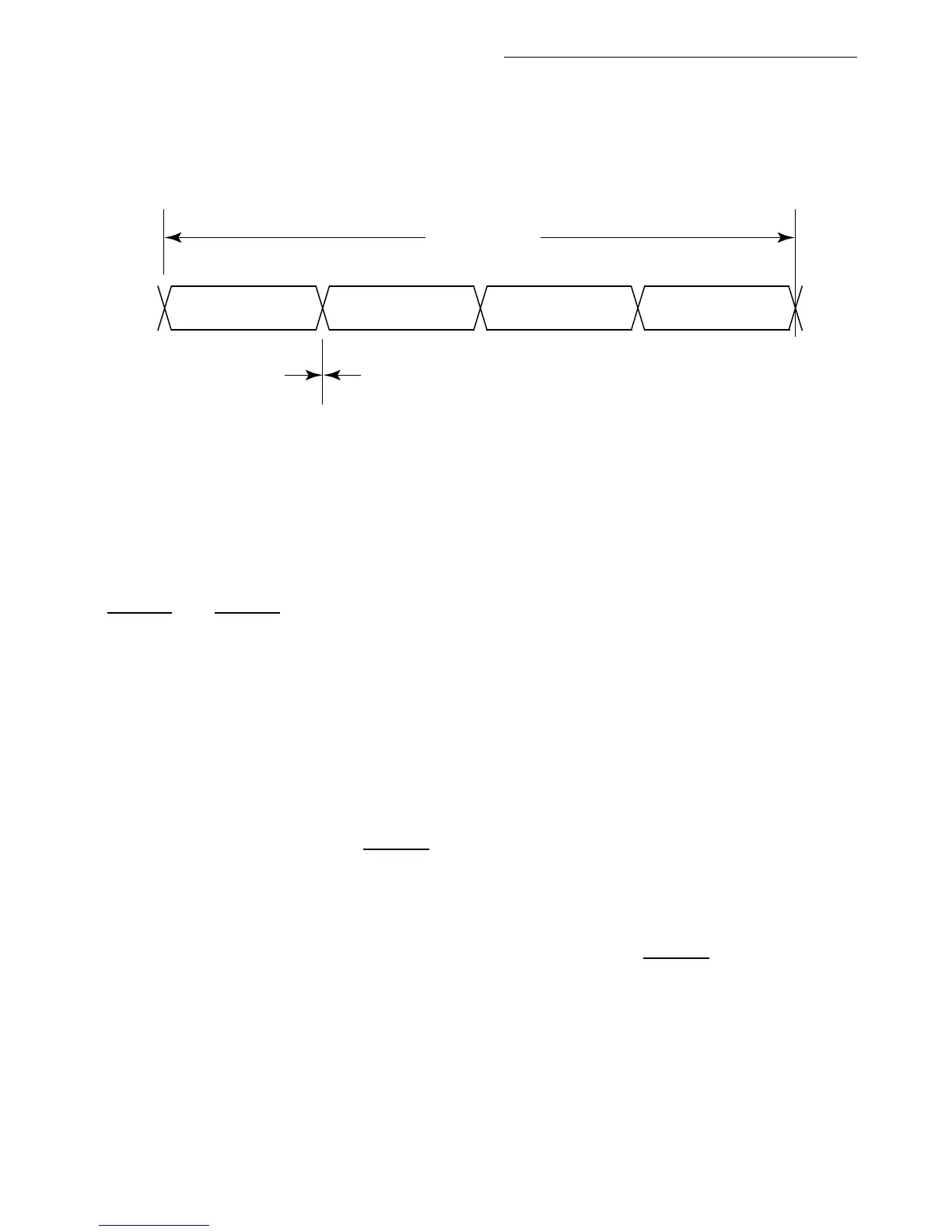

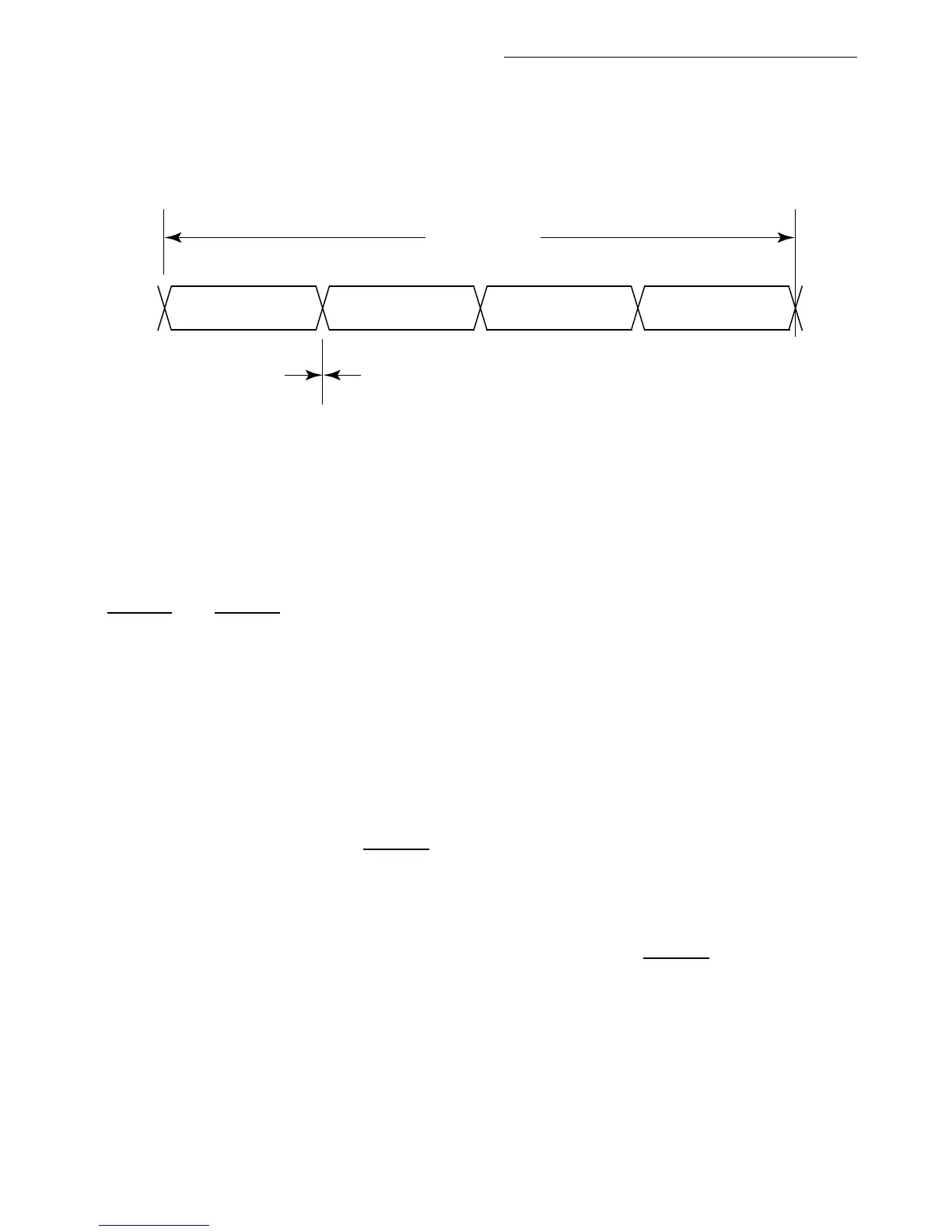

Figure 6-11. Burst Operation Cycles and Burst Mode

(UNABLE TO LOCATE ART)

Figure 6-12. Burst Filling Wraparound Example

(UNABLE TO LOCATE ART)

Figure 6-13. Deferred Burst Filling Example

FIRST ACCESS OF BURST

OPERATION REQUIRED

OPERAND OR PREFETCH

BURST FILL CYCLE BURST FILL CYCLE BURST FILL CYCLE

CYCLE 1 CYCLE 2 CYCLE 3 CYCLE 4

BURST MODE

REQUESTED AND

ACKNOWLEDGED

BURST MODE BEGINS HERE

BURST OPERATION

Loading...

Loading...