Introduction

1-8

MC68030 USER’S MANUAL

MOTOROLA

Alternate function code registers, SFC and DFC, contain 3-bit function codes. Function

codes can be considered extensions of the 32-bit linear address that optionally provide as

many as eight 4-Gbyte address spaces. Function codes are automatically generated by the

processor to select address spaces for data and program at the user and supervisor

privilege levels and a CPU address space for processor functions (e.g., coprocessor

communications). Registers SFC and DFC are used by certain instructions to explicitly

specify the function codes for operations.

The cache control register (CACR) controls the on-chip instruction and data caches of the

MC68030. The cache address register (CAAR) stores an address for cache control

functions.

The CPU root pointer (CRP) contains a pointer to the root of the translation tree for the

currently executing task of the MC68030. This tree contains the mapping information for the

task's address space. When the MC68030 is configured to provide a separate address

space for supervisor routines, the supervisor root pointer (SRP) contains a pointer to the root

of the translation tree describing the supervisor's address space.

The translation control register (TC) consists of several fields that control address

translation. These fields enable and disable address translation, enable and disable the use

of SRP for the supervisor address space, and select or ignore the function codes in

translating addresses. Other fields define the size of memory pages, the number of address

bits used in translation, and the translation table structure.

The transparent translation registers, TT0 and TT1, can each specify separate blocks of

memory as directly accessible without address translation. Logical addresses in these areas

become the physical addresses for memory access. Function codes and the eight most

significant bits of the address can be used to define the area of memory and type of access;

either read, write, or both types of memory access can be directly mapped. The transparent

translation feature allows rapid movement of large blocks of data in memory or I/O space

without disturbing the context of the on-chip address translation cache or incurring delays

associated with translation table lookups. This feature is useful to graphics, controller, and

real-time applications.

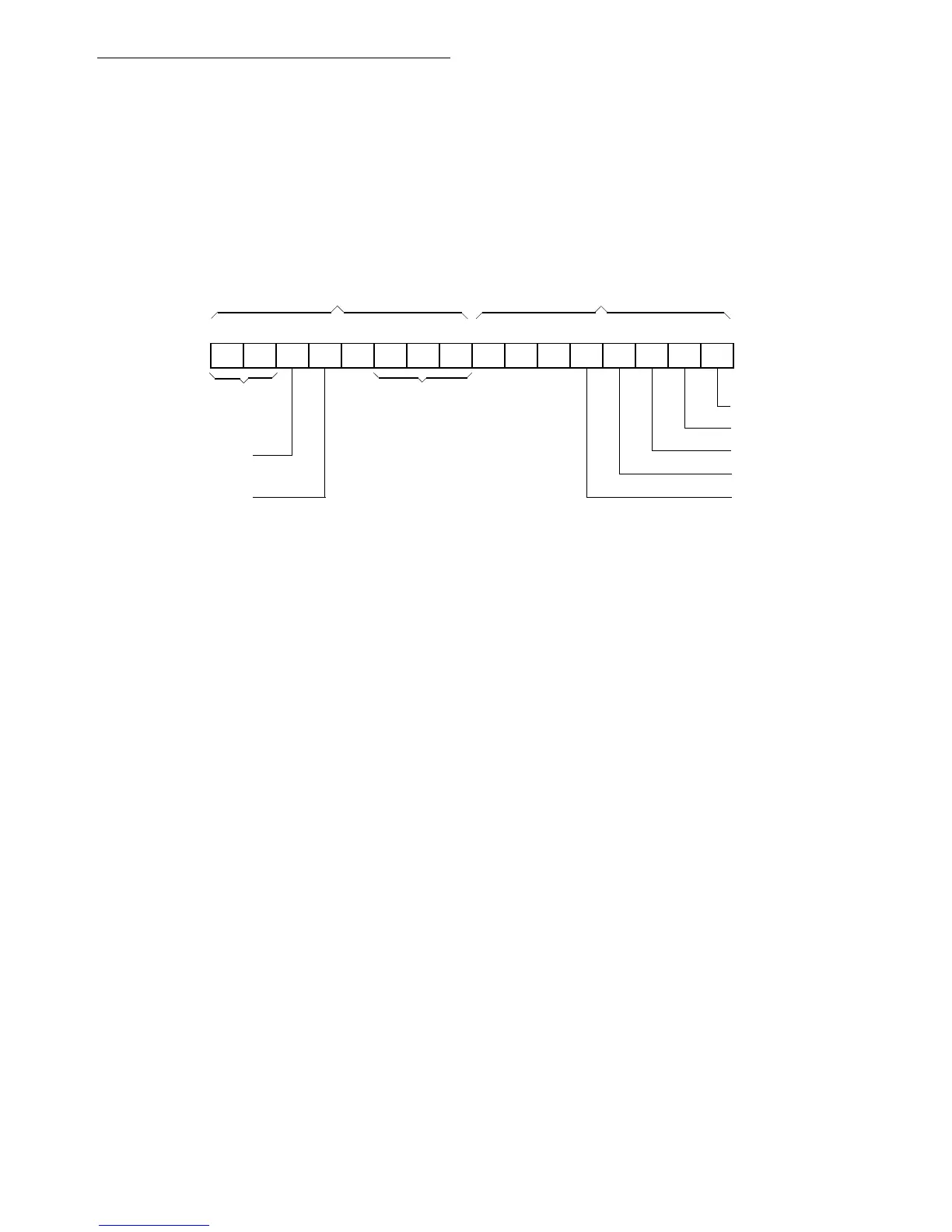

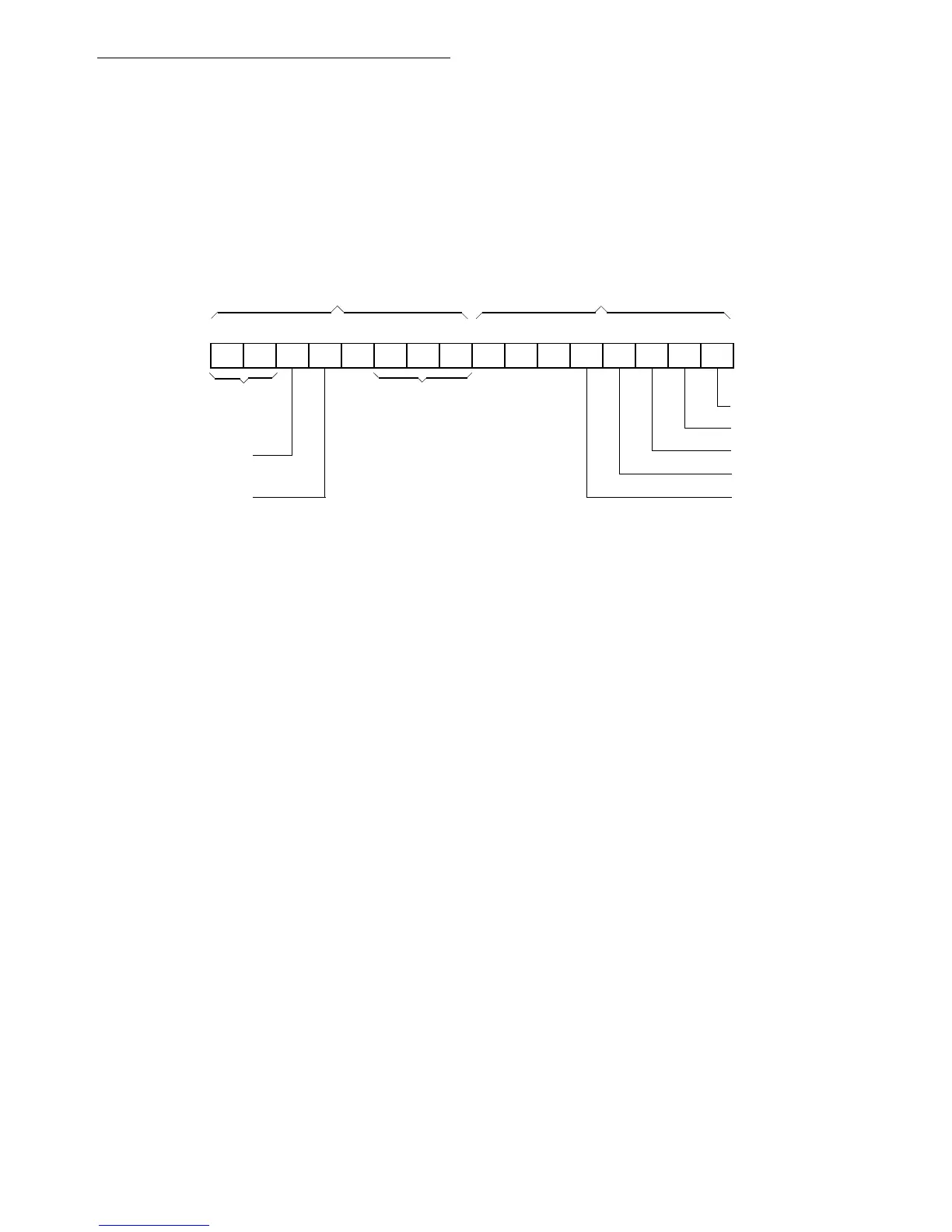

Figure 1-4. Status Register

T1 T0 S M 0 I2 I1 I0 X N Z V C000

SYSTEM BYTE

USER BYTE

(CONDITION CODE REGISTER)

TRACE

ENABLE

INTERRUPT

PRIORITY MASK

SUPERVISOR/USER

STATE

MASTER/INTERRUPT

STATE

EXTEND

NEGATIVE

ZERO

OVERFLOW

CARRY

15 14 13 12 11 10 9 8 7 56 43210

Loading...

Loading...