Bus Operation

7-98 MC68030 USER’S MANUAL MOTOROLA

7.7 BUS ARBITRATION

The bus design of the MC68030 provides for a single bus master at any one time: either the

processor or an external device. One or more of the external devices on the bus can have

the capability of becoming bus master. Bus arbitration is the protocol by which an external

device becomes bus master; the bus controller in the MC68030 manages the bus arbitration

signals so that the processor has the lowest priority. External devices that need to obtain the

bus must assert the bus arbitration signals in the sequences described in the following

paragraphs. Systems having several devices that can become bus master require external

circuitry to assign priorities to the device so that, when two or more external devices attempt

to become bus master at the same time, the one having the highest priority becomes bus

master first. The sequence of the protocol is:

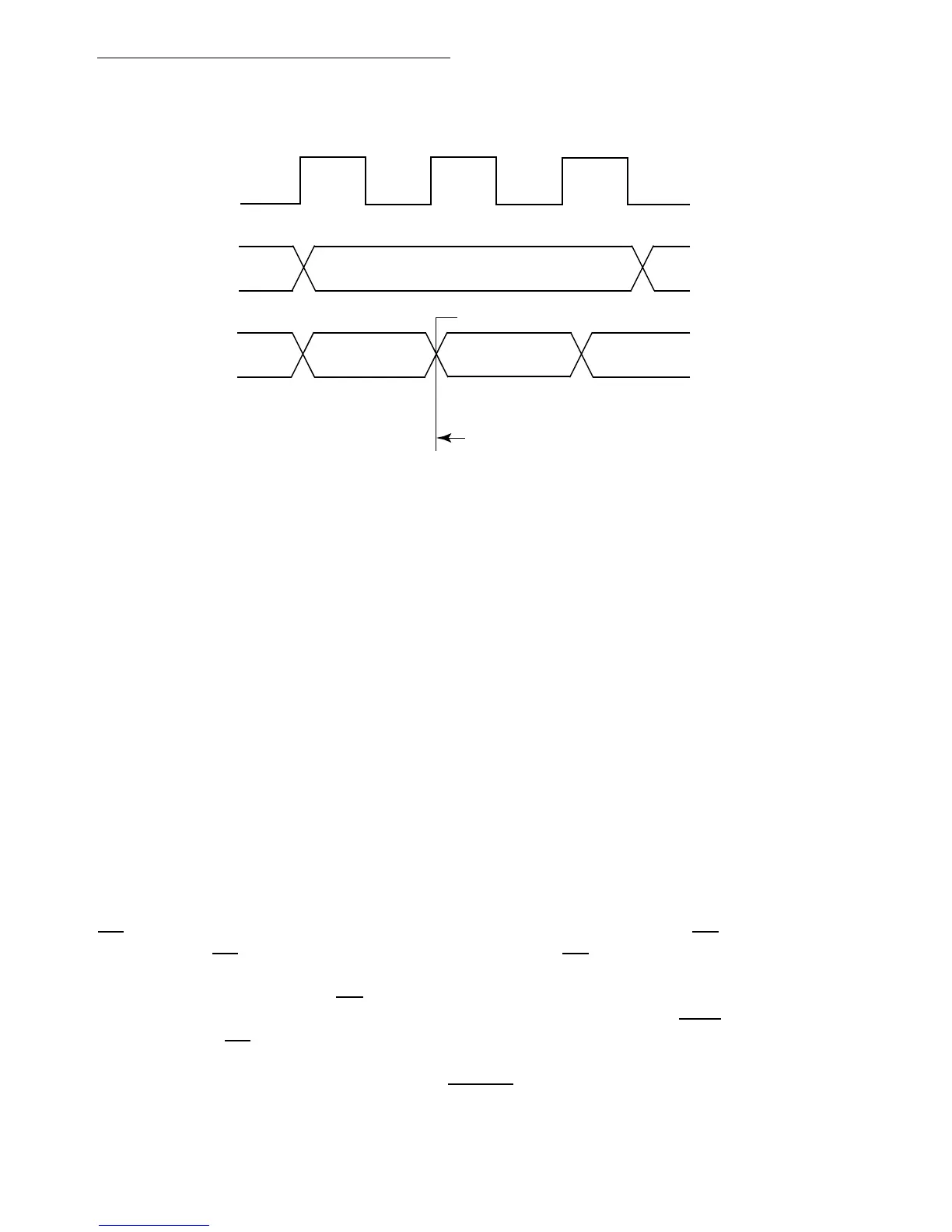

1. An external device asserts the bus request signal.

2. The processor asserts the bus grant signal to indicate that the bus will become avail-

able at the end of the current bus cycle.

3. The external device asserts the bus grant acknowledge signal to indicate that it has

assumed bus mastership.

BR

may be issued any time during a bus cycle or between cycles. BG is asserted in

response to BR

; it is usually asserted as soon as BR has been synchronized and

recognized, except when the MC68030 has made an internal decision to execute a bus

cycle. Then, the assertion of BG

is deferred until the bus cycle has begun. Additionally, BG

is not asserted until the end of a read-modify-write operation (when RMC

is negated) in

response to a BR

signal. When the requesting device receives BG and more than one

external device can be bus master, the requesting device should begin whatever arbitration

is required. The external device asserts BGACK

when it assumes bus mastership and

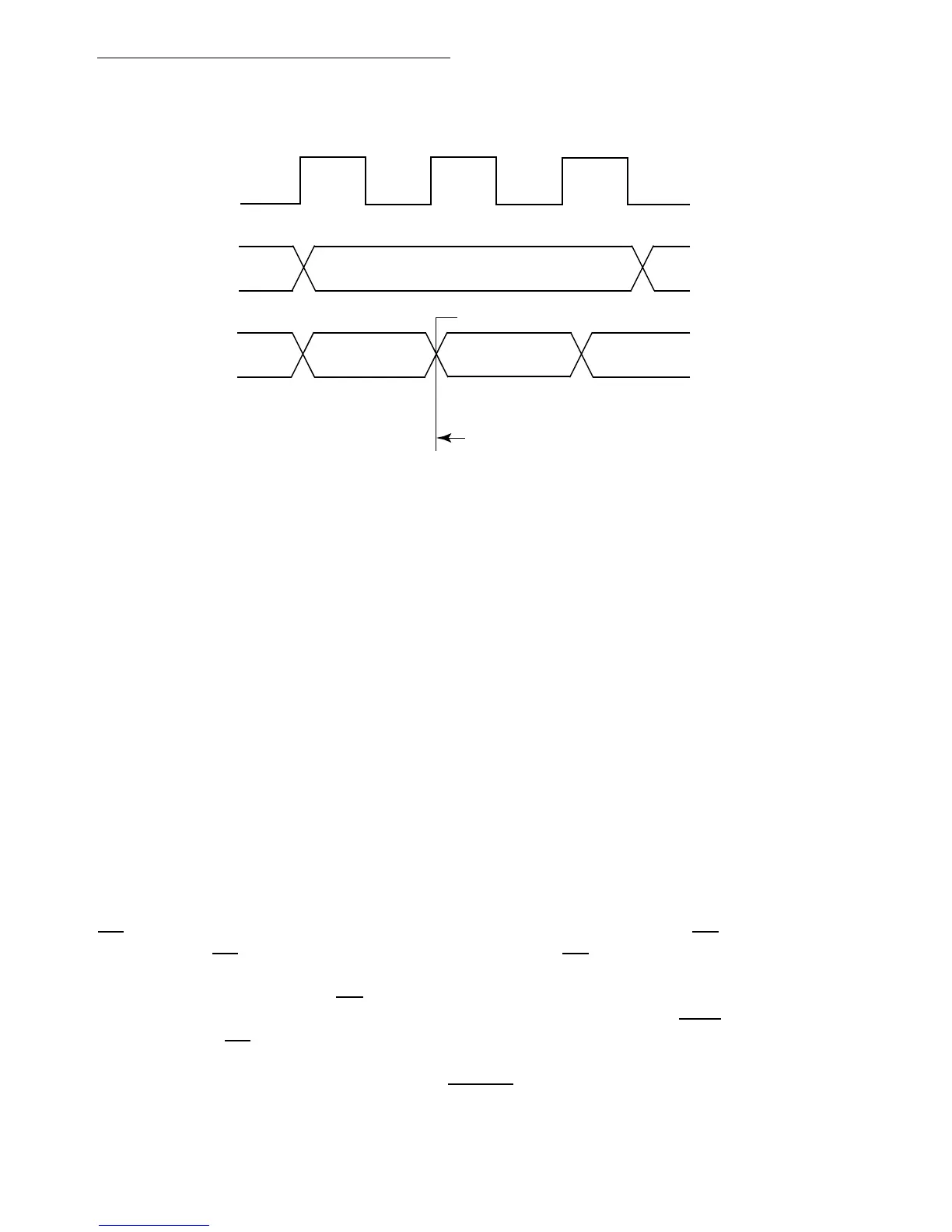

Figure 7-58. Bus Synchronization Example

S0 Sw

EXTERNAL WRITE

WRITE TO D. CACHE D. CACHE READ

MOVE. L D0, (A0)

NOP PREVENTS EXECUTION OF SUBSEQUENT

INSTRUCTIONS UNTIL MOVE. L D0, (A0)

WRITE CYCLE COMPLETES

MOVE . L (A0), D1

Loading...

Loading...