Bus Operation

7-100 MC68030 USER’S MANUAL MOTOROLA

7.7.1 Bus Request

External devices capable of becoming bus masters request the bus by asserting BR. This

can be a wire-ORed signal (although it need not be constructed from open-collector devices)

that indicates to the processor that some external device requires control of the bus. The

processor is effectively at a lower bus priority level than the external device and relinquishes

the bus after it has completed the current bus cycle (if one has started).

If no acknowledge is received while the BR

is active, the processor remains bus master once

BR

is negated. This prevents unnecessary interference with ordinary processing if the

arbitration circuitry inadvertently responds to noise or if an external device determines that

it no longer requires use of the bus before it has been granted mastership.

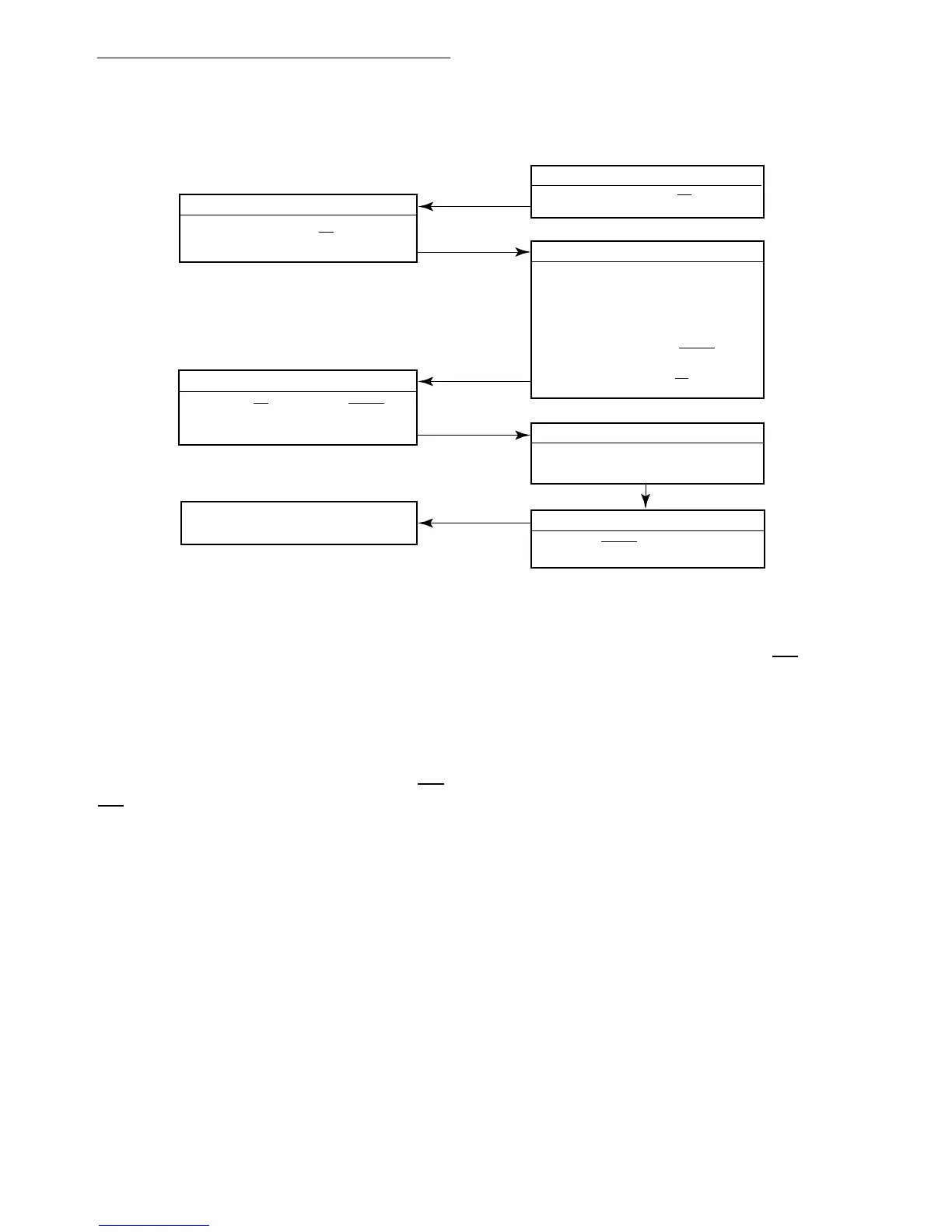

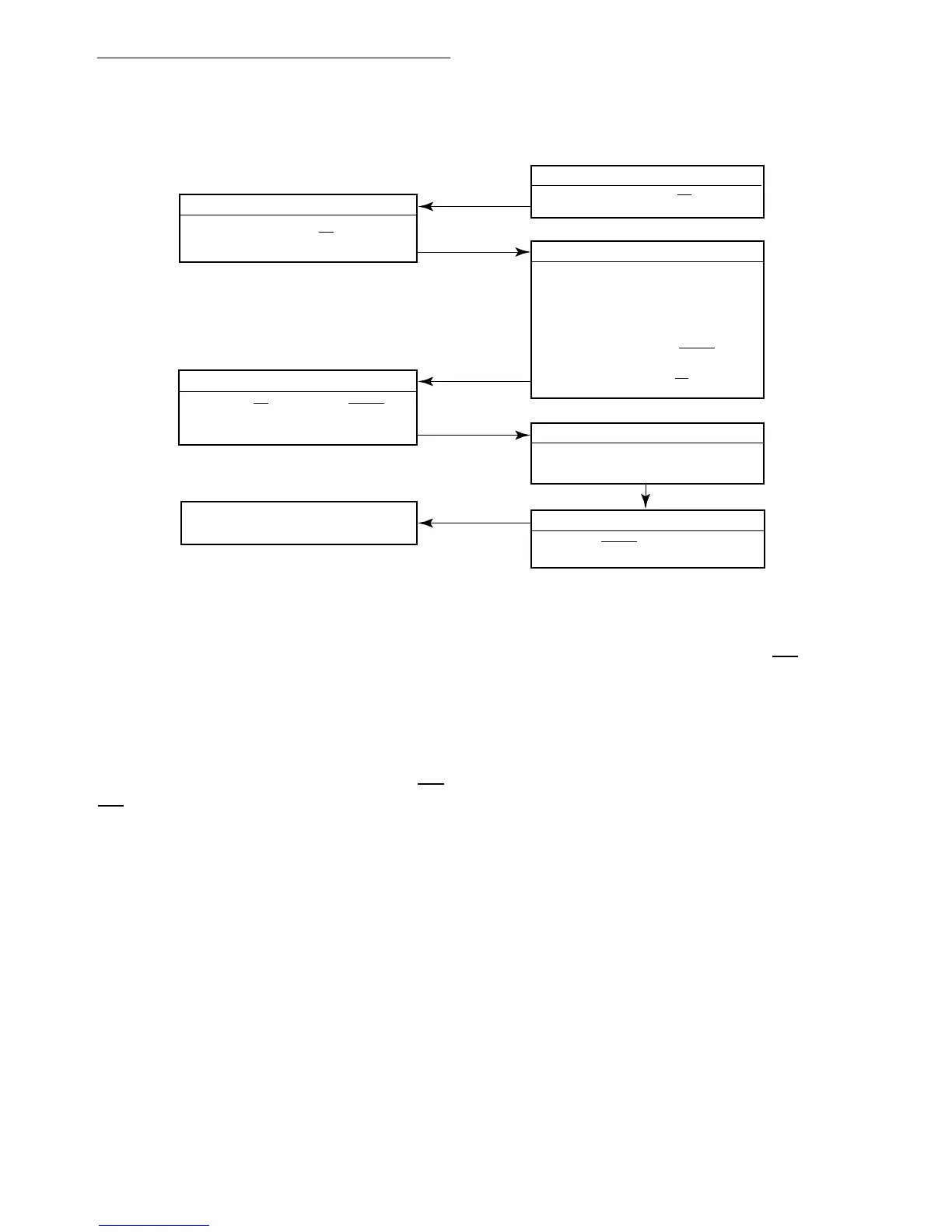

Figure 7-59. Bus Arbitration Flowchart for Single Request

1) ASSERT BUS GRANT (BG)

GRANT BUS ARBITRATION

TERMINATE ARBITRATION

1) NEGATE BG AND WAIT FOR BGACK TO

BE NEGATED

REARBITRATE OR RESUME

CONTROLLER OPERATION

REQUEST THE BUS

1) ASSERT BUS REQUEST (BR)

REQUESTING DEVICECONTROLLER

ACKNOWLEDGE BUS MASTERSHIP

1) EXTERNAL ARBITRATION DETERMINES

NEXT BUS MASTER

2) NEXT BUS MASTER WAITS FOR

CURRENT CYCLE TO COMPLETE

3) NEXT BUS MASTER ASSERTS BUS

GRANT ACKNOWLEDGE (BGACK) TO

BECOME NEW MASTER

4) BUS MASTER NEGATES BR

OPERATE AS BUS MASTER

RELEASE BUS MASTERSHIP

1) PERFORM DATA TRANSFERS

(READ AND WRITE CYCLES)

1) NEGATE BGACK

Loading...

Loading...