Bus Operation

MOTOROLA

MC68030 USER’S MANUAL

7-3

A device with a 32-bit port size can also provide a synchronous mode transfer. In

synchronous operation, input signals are externally synchronized to the processor clock,

and the synchronizing delay is not incurred.

Synchronous inputs (STERM

, CBACK, and CIIN) must remain stable during a sample

window for all rising edges of the clock during a bus cycle (i.e., while address strobe (AS

) is

asserted), regardless of when the signals are asserted or negated, to ensure proper

operation. This sample window is defined by the synchronous input setup and hold times

(see MC68030EC/D,

MC68030 Electrical Specifications

).

7.1.1 Bus Control Signals

The external cycle start (ECS) signal is the earliest indication that the processor is initiating

a bus cycle. The MC68030 initiates a bus cycle by driving the address, size, function code,

read/write, and cache inhibit-out outputs and by asserting ECS

. However, if the processor

finds the required program or data item in an on-chip cache, if a miss occurs in the address

translation cache (ATC) of the memory management unit (MMU), or if the MMU finds a fault

with the access, the processor aborts the cycle before asserting AS

. ECS can be used to

initiate various timing sequences that are eventually qualified with AS

. Qualification with AS

may be required since, in the case of an internal cache hit, an ATC miss, or an MMU fault,

a bus cycle may be aborted after ECS

has been asserted. The assertion of AS ensures that

the cycle has not been aborted by these internal conditions.

During the first external bus cycle of an operand transfer, the operand cycle start (OCS

)

signal is asserted with ECS

. When several bus cycles are required to transfer the entire

operand, OCS

is asserted only at the beginning of the first external bus cycle. With respect

to OCS

, an "operand'' is any entity required by the execution unit, whether a program or data

item.

The function code signals (FC0–FC2) are also driven at the beginning of a bus cycle. These

three signals select one of eight address spaces (refer to Table 4-1) to which the address

applies. Five address spaces are presently defined. Of the remaining three, one is reserved

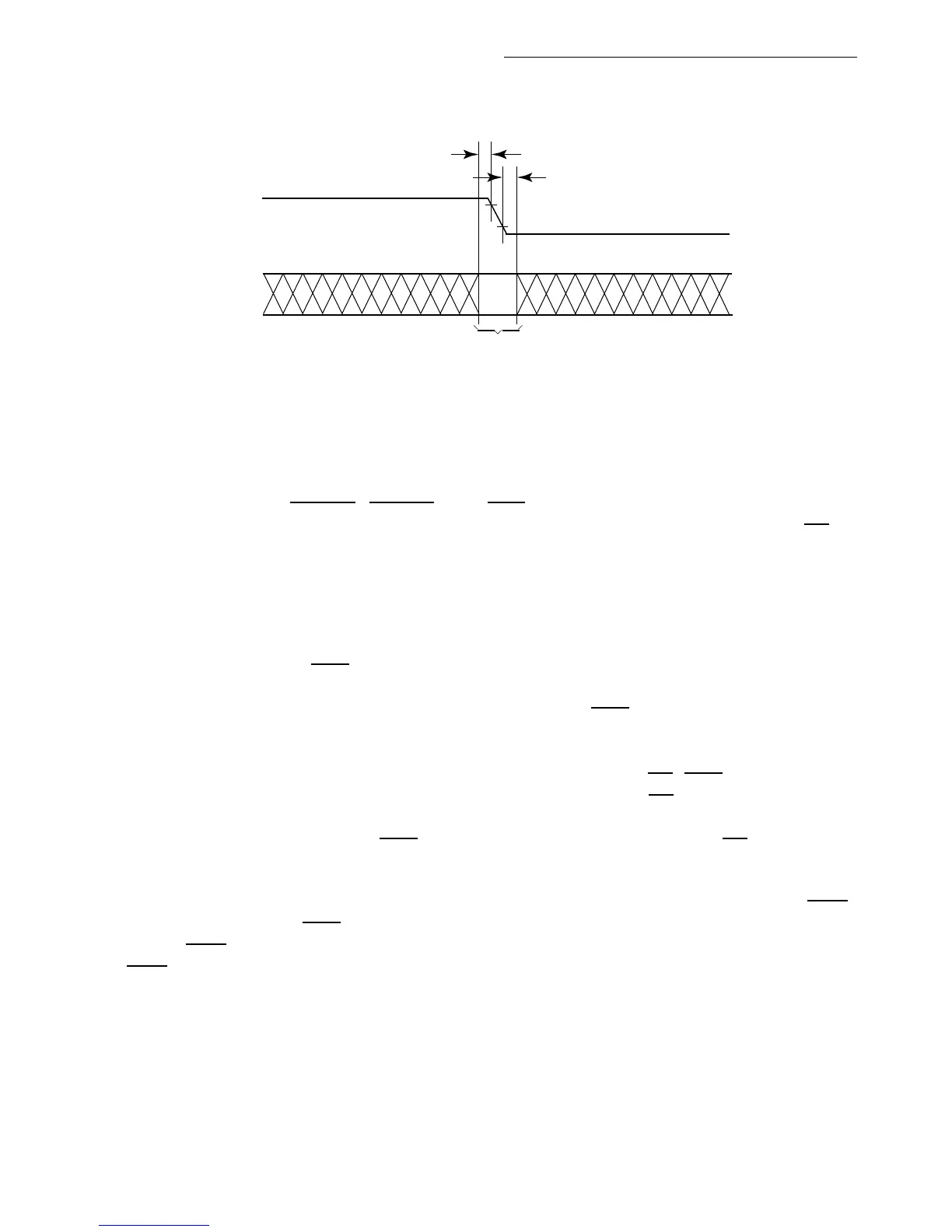

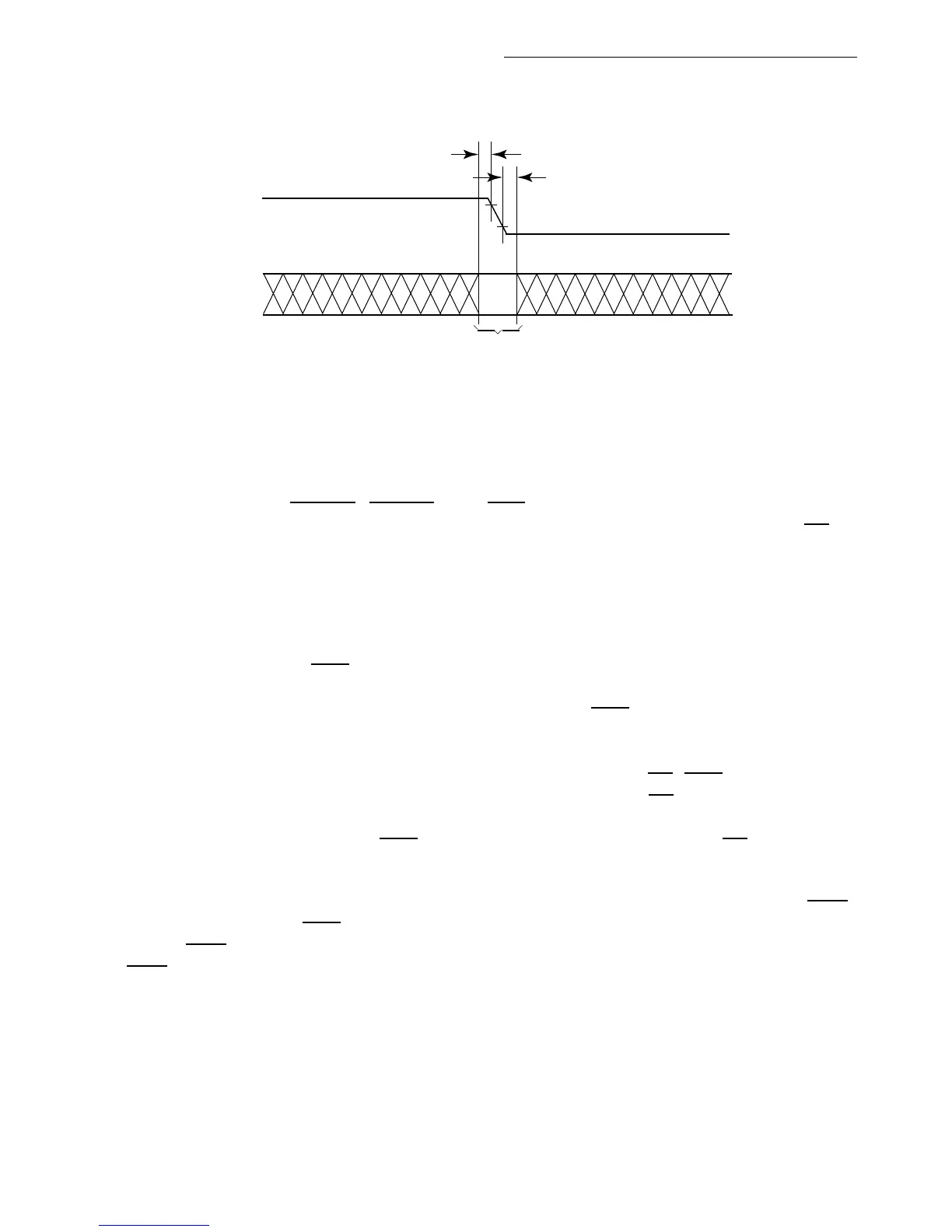

Figure 7-2. Asynchronous Input Sample Window

t

su

t

h

SAMPLE

WINDOW

CLK

EXT

Loading...

Loading...