Data Organization and Addressing Capabilities

2-38 MC68030 USER’S MANUAL MOTOROLA

2.8.2 User Program Stacks

The user can implement stacks with the address register indirect with postincrement and

predecrement addressing modes. With address register An (n = 0–6), the user can

implement a stack that is filled wither from high to low memory or from low to high memory.

Important considerations are:

• Use the predecrement mode to decrement the register before its contents are used as

the pointer to the stack.

• Use the postincrement mode to increment the register after its contents are used as the

pointer to the stack.

• Maintain the stack pointer correctly when byte, word, and long-word items are mixed in

these stacks.

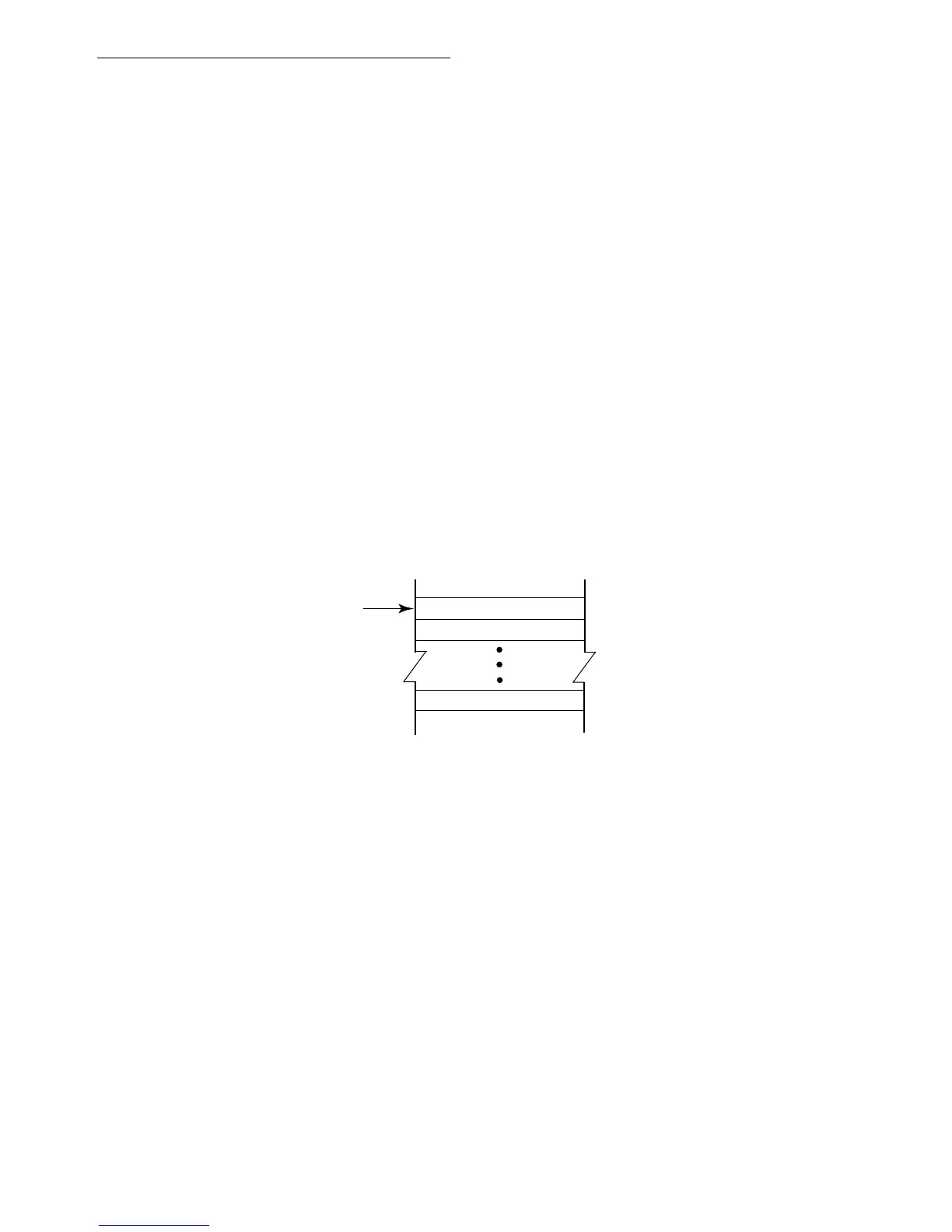

To implement stack growth from high to low memory, use:

–(An) to push data on the stack,

(An)+ to pull data from the stack.

For this type of stack, after either a push or a pull operation, register An points to the top item

on the stack. This is illustrated as:

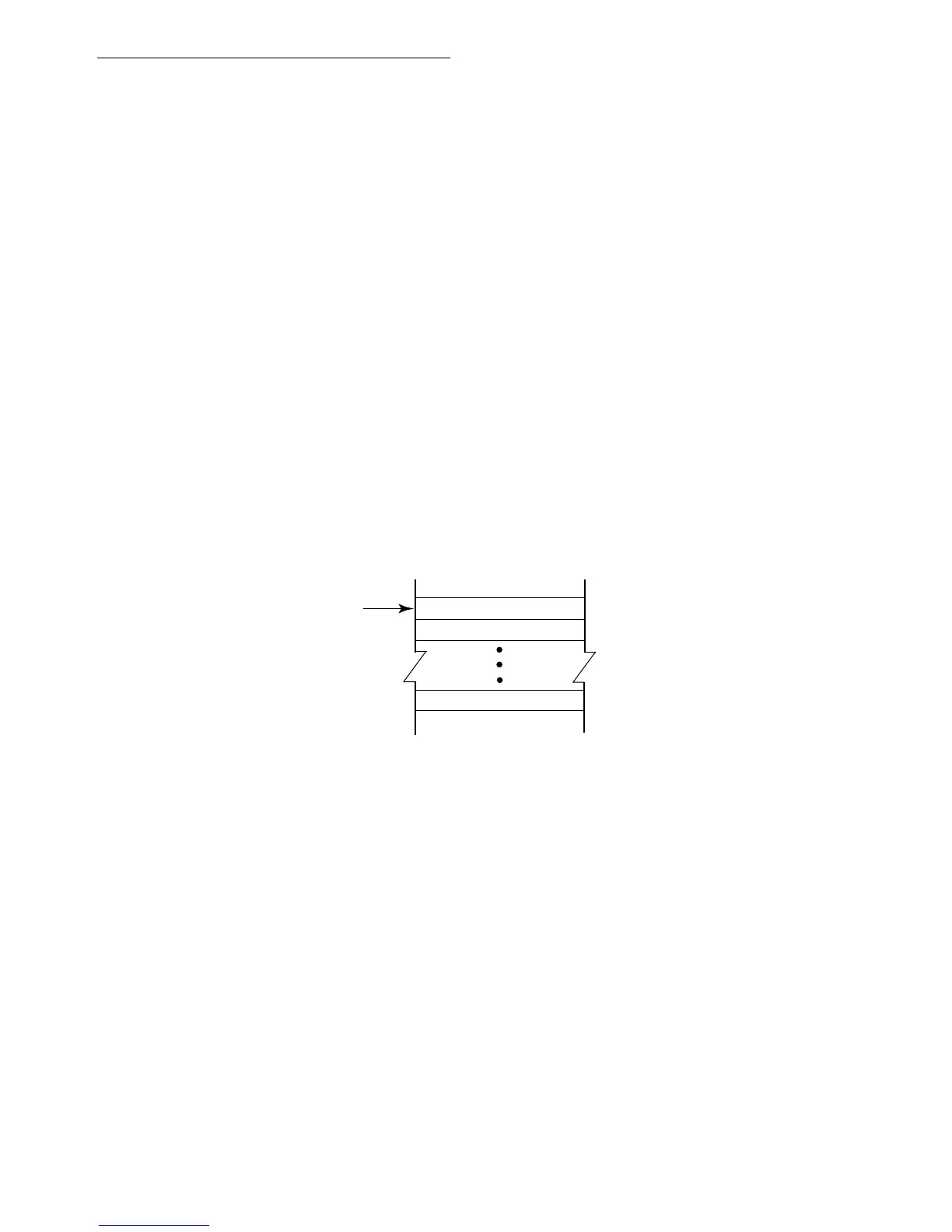

To implement stack growth from low to high memory, use:

(An)+ to push data on the stack,

–An to pull data from the stack.

An

LOW MEMORY

(FREE)

TOP OF STACK

BOTTOM OF STACK

HIGH MEMORY

Loading...

Loading...