Data Organization and Addressing Capabilities

2-18 MC68030 USER’S MANUAL MOTOROLA

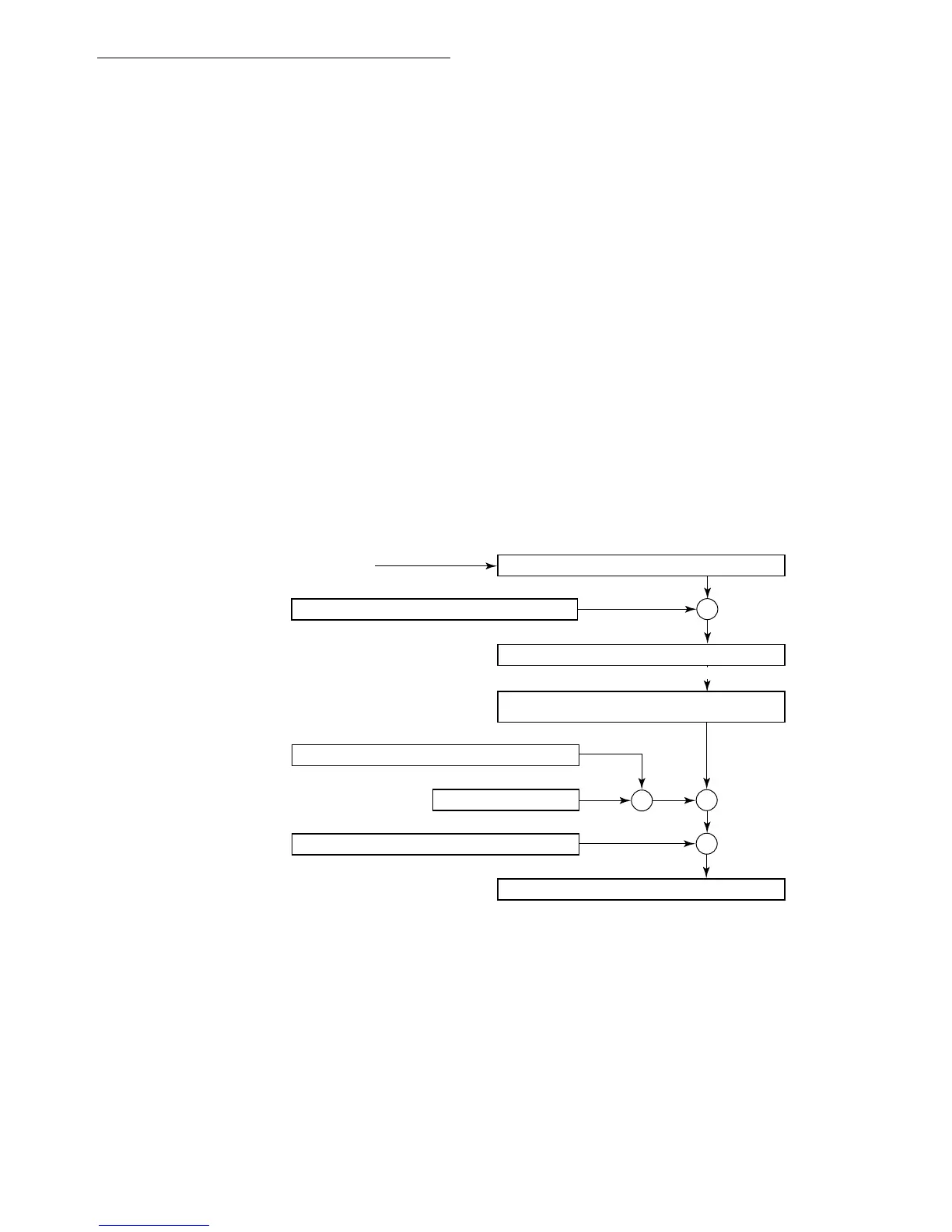

2.4.14 Program Counter Memory Indirect Postindexed Mode

This mode is similar to the memory indirect postindexed mode described in 2.4.9 Memory

Indirect Postindexed Mode, but the PC is used as the base register. Both the operand and

operand address are in memory. The processor calculates an intermediate indirect memory

address by adding a base displacement (bd) to the PC contents. The processor accesses a

long word at that address and adds the scaled contents of the index register and the optional

outer displacement (od) to yield the effective address. The value of the PC used in the

calculation is the address of the first extension word. The reference is a program space

reference and is only allowed for reads (refer to 4.2 Address Space Types).

In the syntax for this mode, brackets enclose the values used to calculate the intermediate

memory address. All four user-specified values are optional. However, the user must supply

the assembler notation ZPC (zero value is taken for the PC) to indicate that the PC is not

used. This allows the user to access the program space without using the PC in calculating

the effective address. Both the base and outer displacements may be null, word, or long

word. When a displacement is omitted or an element is suppressed, its value is taken as

zero in the effective address calculation.

31 0

31 0

31 0

31 0

31 0

31 0

EFFECTIVE ADDRESS:

NUMBER OF EXTENSION WORDS: 1,2, 3, 4, OR 5

EA = (bd + PC) + Xn.SIZE*SCALE + od

([bd, PC], Xn.SIZE*SCALE,od)

111

011

GENERATION:

ASSEMBLER SYNTAX:

MODE:

REGISTER FIELD:

PROGRAM COUNTER:

SIGN-EXTENDED VALUE

SCALE VALUE

OPERAND

+

+

31

0

BASE DISPLACEMENT:

INDEX REGISTER:

MEMORY ADDRESS

INDIRECT MEMORY ADDRESS

VALUE AT INDIRECT MEMORY

ADDRESS IN PROGRAM SPACE

POINTS TO

SIGN-EXTENDED VALUE

SIGN-EXTENDED VALUE

+

X

OUTER DISPLACEMENT:

07

Loading...

Loading...