122 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

Using the TX Receiver Detection for PCI Express

While in the P1 power state, the GTP transceiver can be instructed to perform a receiver detection

operation to determine if there is a receiver at the other end of the link. Figure 3-23 shows an

example use mode on how to perform receiver detection in PCI Express mode.

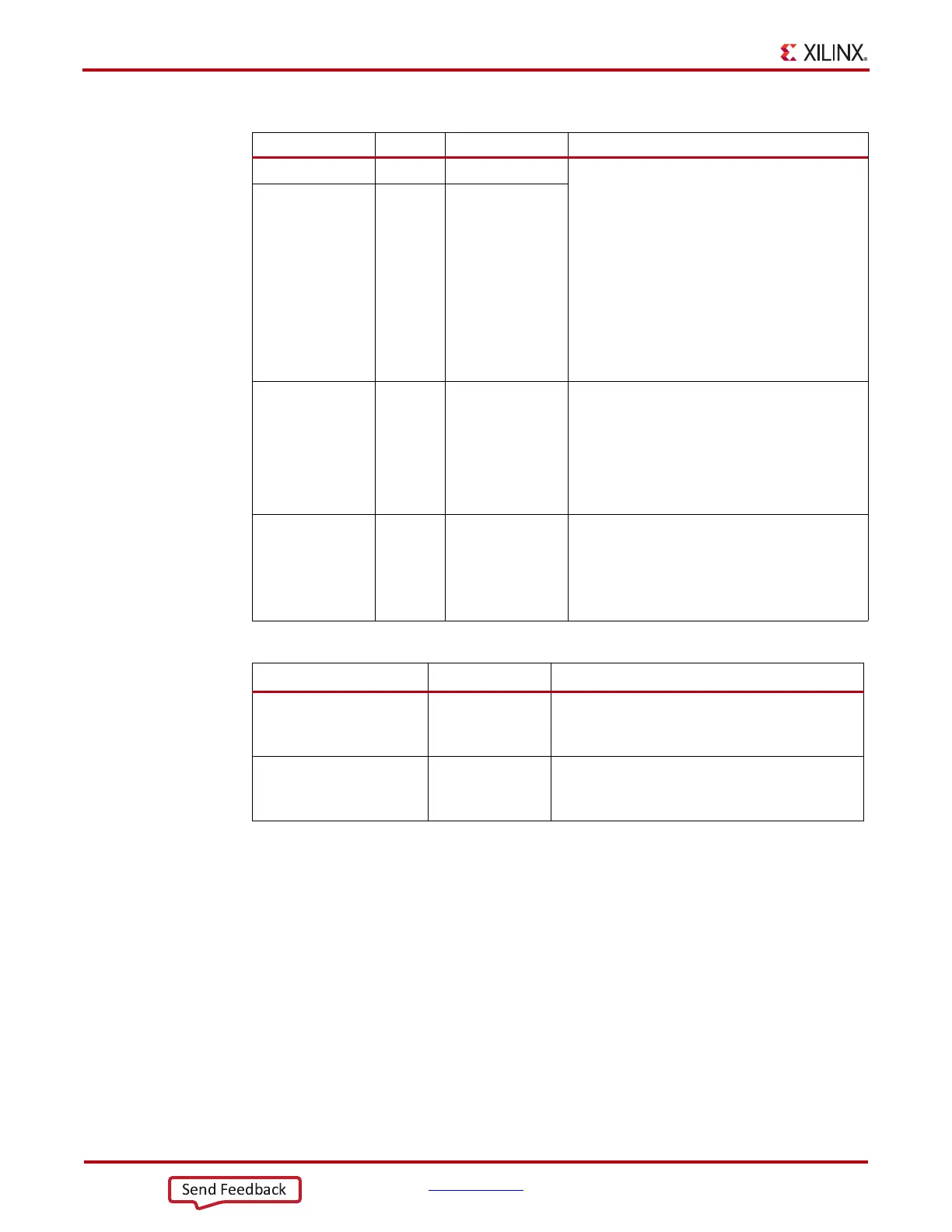

TXPD[1:0] In TXUSRCLK2 Power up or down the TX and RX of the GTP

transceiver. In PCI Express mode, TXPD and

RXPD should be tied to the same source. To

perform receiver detection, set these signals to

the P1 power saving state.

00: P0 power state for normal operation.

01: P0s power saving state with low recovery

time latency.

10: P1 power saving state with longer

recovery time latency.

11: P2 power saving state with lowest power.

RXPD[1:0] In RXUSRCLK2

PHYSTATUS Out RXUSRCLK2 In PCI Express mode, this signal is used to

communicate completion of several GTP

transceiver functions, including power

management state transitions, rate change, and

receiver detection. During receiver detection,

this signal is asserted High to indicate receiver

detection completion.

RXSTATUS[2:0] Out RXUSRCLK2 During receiver detection, this signal is read

when PHYSTATUS is asserted High. Only these

encodings are valid during receiver detection:

000: Receiver not present.

011: Receiver present.

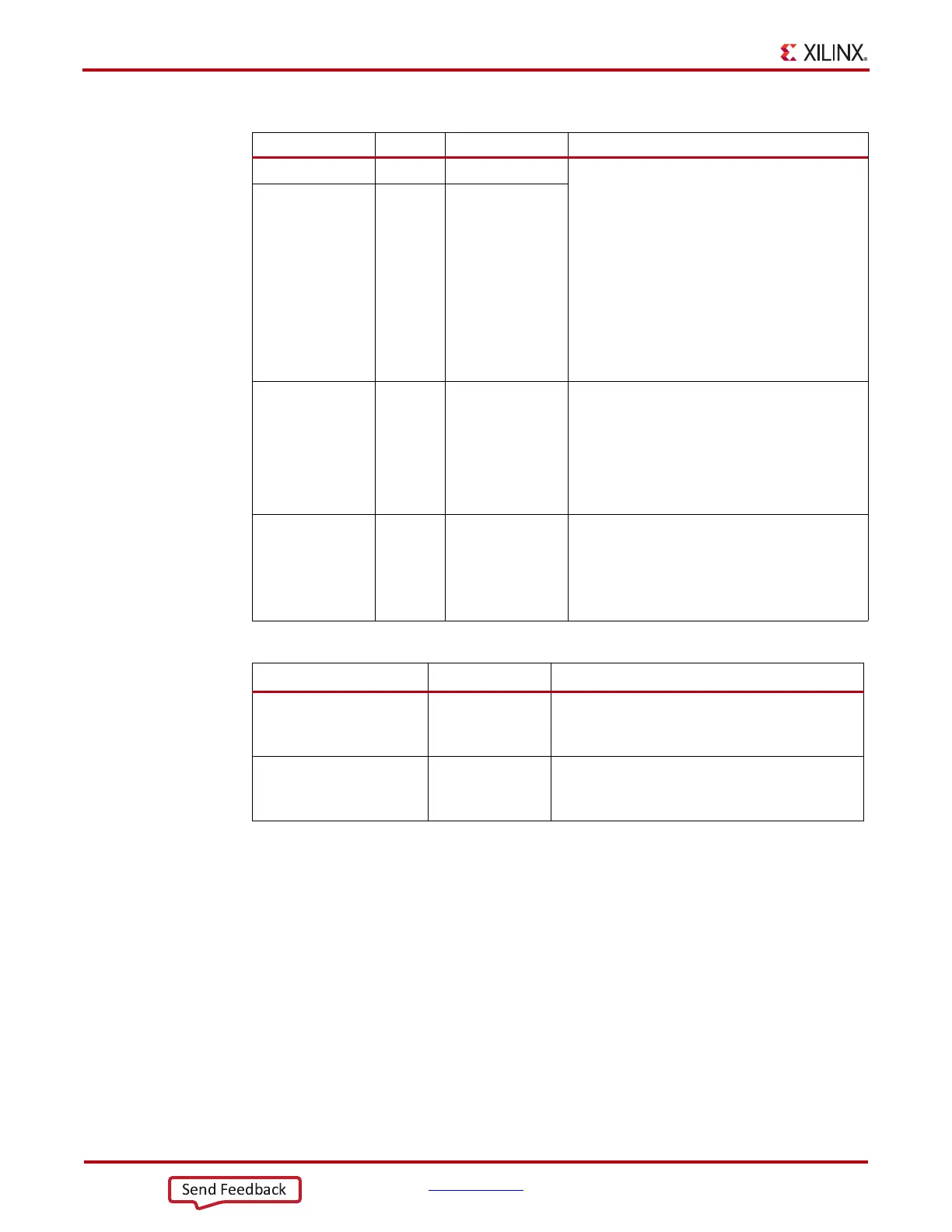

Table 3-31: TX Receiver Detection Attributes

Attribute Type Description

TX_RXDETECT_CFG 14-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

TX_RXDETECT_REF 3-bit Binary Reserved. The recommended value from the

7 Series FPGAs Transceivers Wizard should be

used.

Table 3-30: TX Receiver Detection Ports (Cont’d)

Port Dir Clock Domain Description

Loading...

Loading...