126 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

9. RX Byte and Word Alignment, page 161

10. RX 8B/10B Decoder, page 170

11. RX Buffer Bypass, page 174

12. RX Elastic Buffer, page 187

13. RX Clock Correction, page 191

14. RX Channel Bonding, page 198

15. RX Gearbox, page 207

16. FPGA RX Interface, page 214

RX Analog Front End

Functional Description

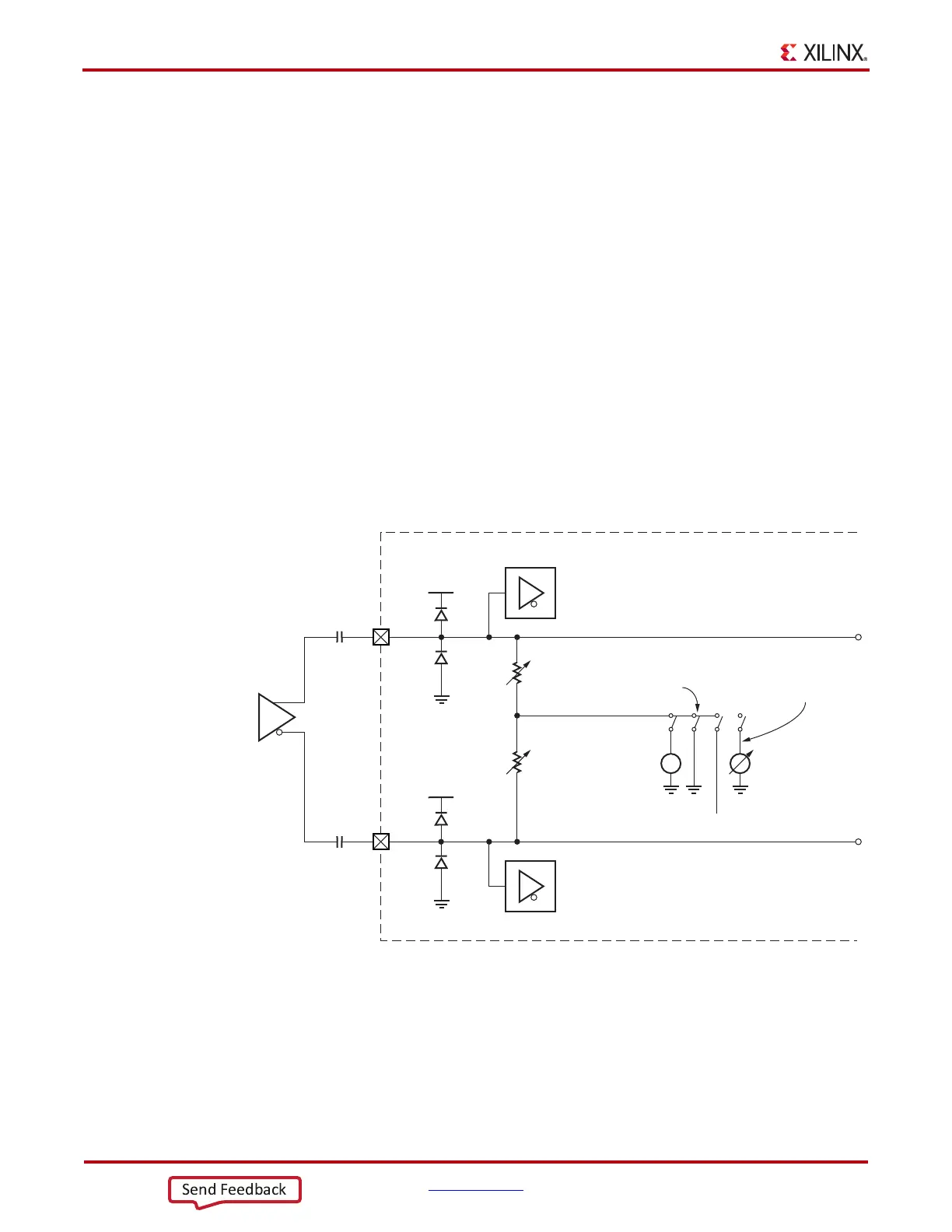

The RX analog front end (AFE) is a high-speed current-mode input differential buffer (see

Figure 4-1). It has these features:

• Configurable RX termination voltage

• Calibrated termination resistors

X-Ref Target - Figure 4-2

Figure 4-2: RX Analog Front End

+

–

+

–

FPGABoard

ACJTAG RX

ACJTAG RX

50Ω

50Ω

MGTAVTT Programmable

GND

FLOAT

MGTAVTT

MGTAVTT

~100 nF

~100 nF

RX_CM_SEL[1:0]

UG482_c4_02_110911

RX_CM_TRIM[3:0]