76 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

5. TX Pattern Generator, page 103

6. TX Pattern Generator, page 103

7. TX Polarity Control, page 106

8. TX Fabric Clock Output Control, page 107

9. TX Configurable Driver, page 114

10. TX Receiver Detect Support for PCI Express Designs, page 121

11. TX Out-of-Band Signaling, page 123

FPGA TX Interface

Functional Description

The FPGA TX interface is the FPGA’s gateway to the TX datapath of the GTP transceiver.

Applications transmit data through the GTP transceiver by writing data to the TXDATA port on the

positive edge of TXUSRCLK2. The width of the port can be configured to be two or four bytes

wide. The actual width of the port depends on the TX_DATA_WIDTH attribute and TX8B10BEN

port setting. Port widths can be 16, 20, 32, and 40 bits. The rate of the parallel clock (TXUSRCLK2)

at the interface is determined by the TX line rate, the width of the TXDATA port, and whether or not

8B/10B encoding is enabled. A second parallel clock (TXUSRCLK) must be provided for the

internal PCS logic in the transmitter. This section shows how to drive the parallel clocks and

explains the constraints on those clocks for correct operation.

Interface Width Configuration

The 7 series FPGA GTP transceiver contains a 2-byte internal datapath. The FPGA interface width

is configurable by setting the TX_DATA_WIDTH attribute. When the 8B/10B encoder is enabled,

the TX_DATA_WIDTH attribute must be configured to 20 bits or 40 bits, and in this case, the FPGA

TX interface only uses the TXDATA ports. For example, TXDATA[15:0] is used when the FPGA

interface width is 16. When the 8B/10B encoder is bypassed, the TX_DATA_WIDTH attribute can

be configured to any of the available widths: 16, 20, 32, or 40 bits.

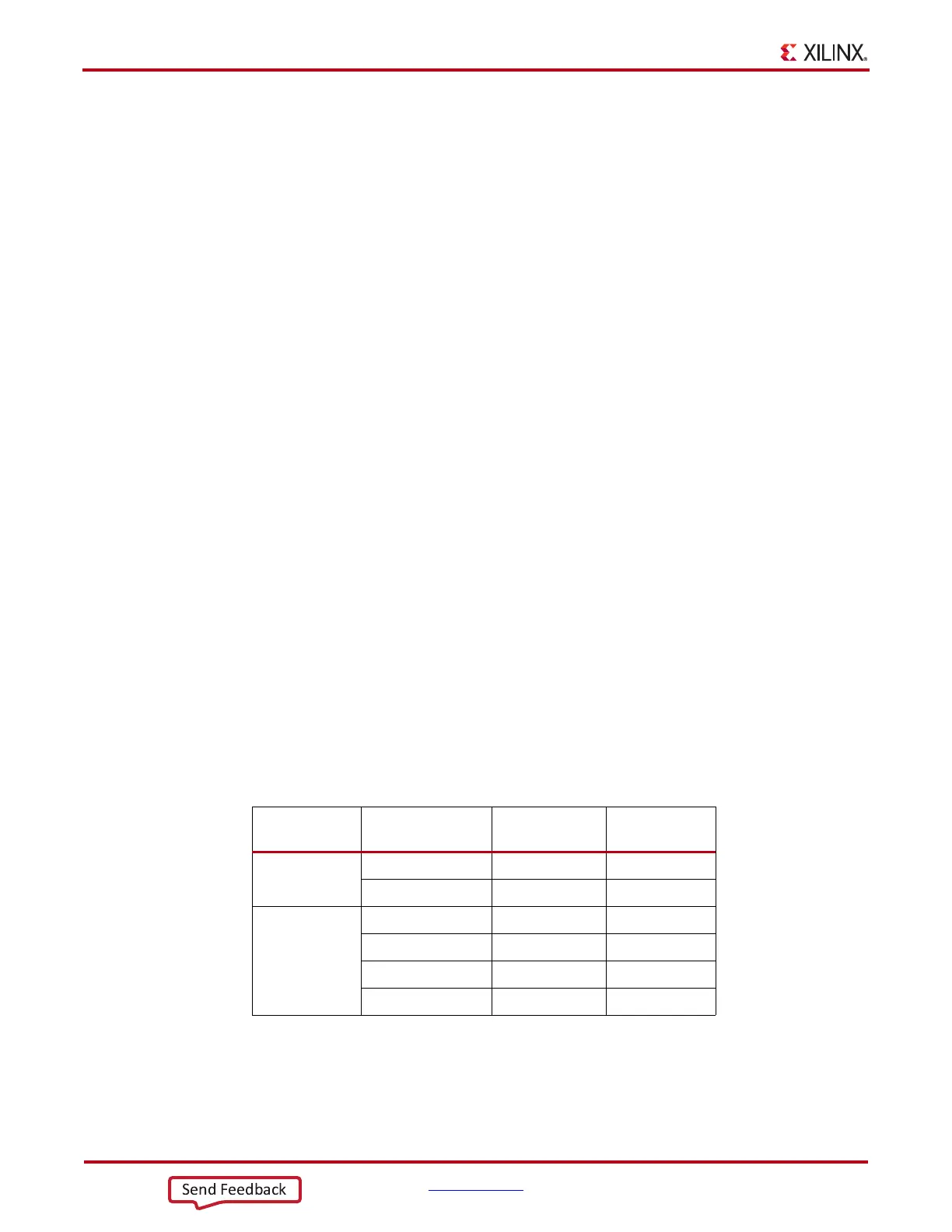

Table 3-1 shows how the interface width for the TX datapath is selected. 8B/10B encoding is

described in more detail in TX 8B/10B Encoder, page 83.

When the 8B/10B encoder is bypassed and the TX_DATA_WIDTH is 20 or 40, the

TXCHARDISPMODE and TXCHARDISPVAL ports are used to extend the TXDATA port from 16

to 20 bits, or 32 to 40 bits. Table 3-2 shows the data transmitted when the 8B/10B encoder is

disabled. When the TX gearbox is used, refer to TX Gearbox, page 86 for data transmission order.

Table 3-1: FPGA TX Interface Datapath Configuration

TX8B10BEN TX_DATA_WIDTH

FPGA Interface

Width

Internal Data

Width

1201620

40 32 20

0161616

20 20 20

32 32 16

40 40 20

Loading...

Loading...