7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 77

UG482 (v1.9) December 19, 2016

FPGA TX Interface

TXUSRCLK and TXUSRCLK2 Generation

The FPGA TX interface includes two parallel clocks: TXUSRCLK and TXUSRCLK2.

TXUSRCLK is the internal clock for the PCS logic in the GTP transceiver transmitter. The required

rate for TXUSRCLK depends on the internal datapath width of the GTPE2_CHANNEL primitive

and the TX line rate of the GTP transceiver transmitter. Equation 3-1 shows how to calculate the

required rate for TXUSRCLK.

Equation 3-1

TXUSRCLK2 is the main synchronization clock for all signals into the TX side of the GTP

transceiver. Most signals into the TX side of the GTP transceiver are sampled on the positive edge

of TXUSRCLK2. TXUSRCLK2 and TXUSRCLK have a fixed-rate relationship based on the

TX_DATA_WIDTH setting. Table 3-3 shows the relationship between TXUSRCLK2 and

TXUSRCLK per TX_DATA_WIDTH value.

These rules about the relationships between clocks must be observed for TXUSRCLK and

TXUSRCLK2:

• TXUSRCLK and TXUSRCLK2 must be positive-edge aligned, with as little skew as possible

between them. As a result, low-skew clock resources (BUFGs and BUFHs) should be used to

drive TXUSRCLK and TXUSRCLK2.

• Even though they might run at different frequencies, TXUSRCLK, TXUSRCLK2, and the

transmitter reference clock must have the same oscillator as their source. Thus TXUSRCLK

and TXUSRCLK2 must be multiplied or divided versions of the transmitter reference clock.

Ports and Attributes

Table 3-4 defines the FPGA TX Interface ports.

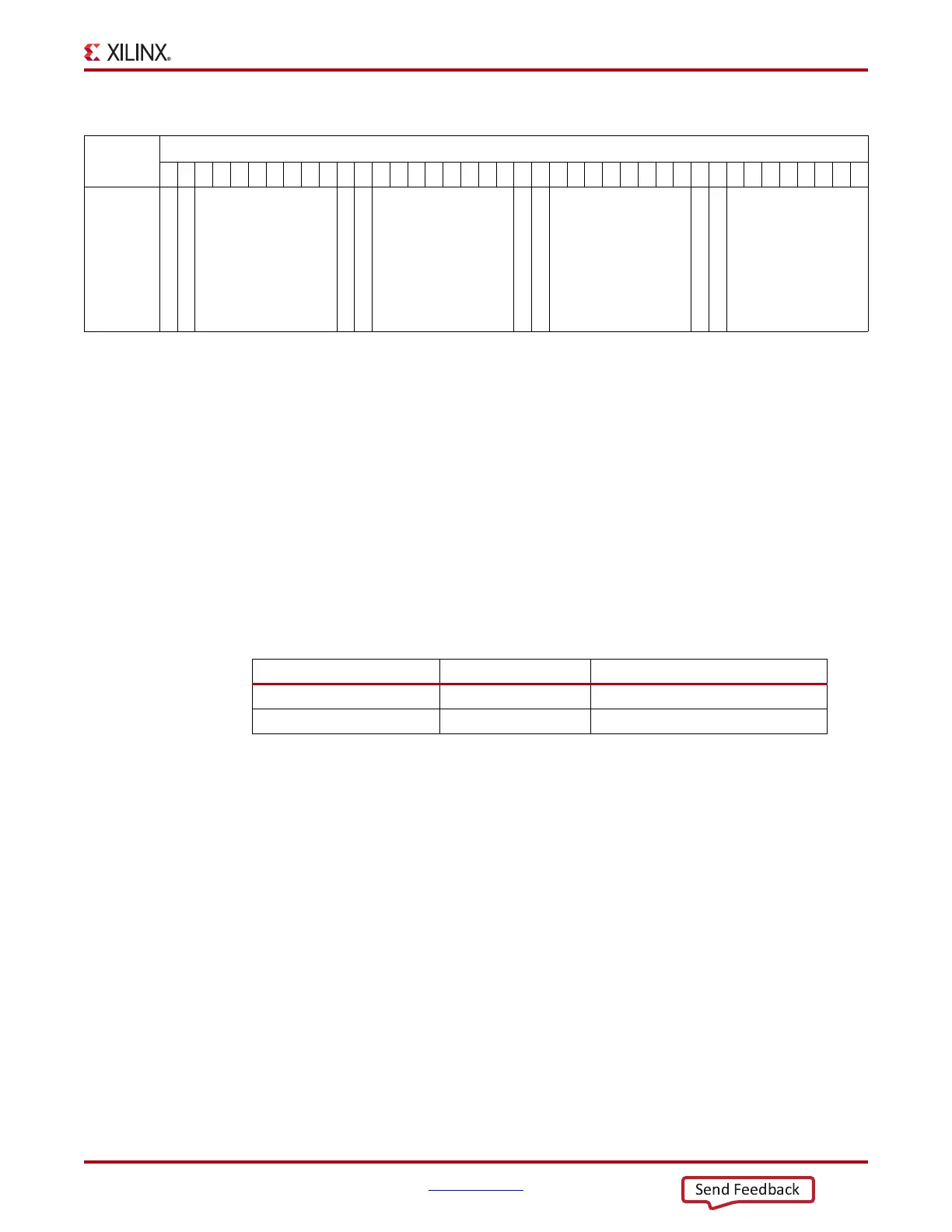

Table 3-2: TX Data Transmitted when 8B/10B Encoder Bypassed

< < < Data Transmission Order is Right to Left (LSB to MSB) < < <

3938373635343332313029282726252423222120191817161514131211109876543210

Data

Transmitted

TXCHARDISPMODE[3]

TXCHARDISPVAL[3]

TXDATA[31:24]

TXCHARDISPMODE[2]

TXCHARDISPVAL[2]

TXDATA[23:16]

TXCHARDISPMODE[1]

TXCHARDISPVAL[1]

TXDATA[15:8]

TXCHARDISPMODE[0]

TXCHARDISPVAL[0]

TXDATA[7:0]

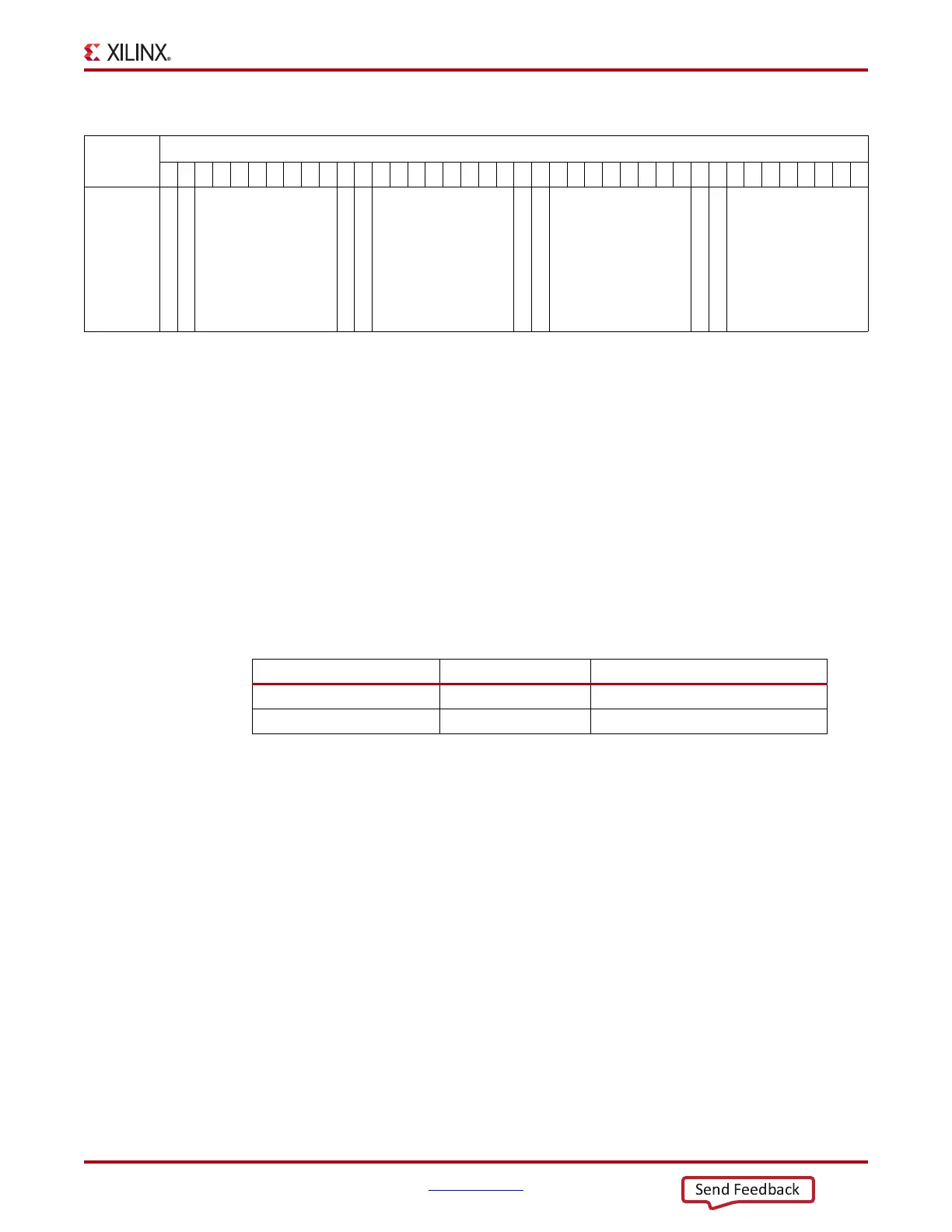

Table 3-3: TXUSRCLK2 Frequency Relationship to TXUSRCLK

FPGA Interface Width TX_DATA_WIDTH TXUSRCLK2 Frequency

2-Byte 16, 20 F

TXUSRCLK2

= F

TXUSRCLK

4-Byte 32, 40 F

TXUSRCLK2

= F

TXUSRCLK

/2

TXUSRCLK Rate

Line Rate

Internal Datapath Width

-------------------------------------------------------------------=

Loading...

Loading...