78 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

Table 3-5 defines the FPGA TX interface attributes.

Using TXOUTCLK to Drive the TX Interface

Depending on the TXUSRCLK and TXUSRCLK2 frequencies, there are different ways FPGA

clock resources can be used to drive the parallel clock for the TX interface. Figure 3-2 through

Figure 3-5 show different ways FPGA clock resources can be used to drive the parallel clocks for

the TX interface. In these examples, the TXOUTCLK is derived from the MGTREFCLK0[P/N] or

MGTREFCLK1[P/N] and the TXOUTCLKSEL = 011 to select the TXPLLREFCLK_DIV1 path as

indicated in Figure 3-20, page 108.

• Depending on the input reference clock frequency and the required line rate, an MMCM and

the appropriate TXOUTCLKSEL port setting is required. The CORE Generator™ tool creates

a sample design based on different design requirements for most cases.

• In use models where TX buffer is bypassed, there are additional restrictions on the clocking

resources. Refer to TX Pattern Generator, page 103 for more information.

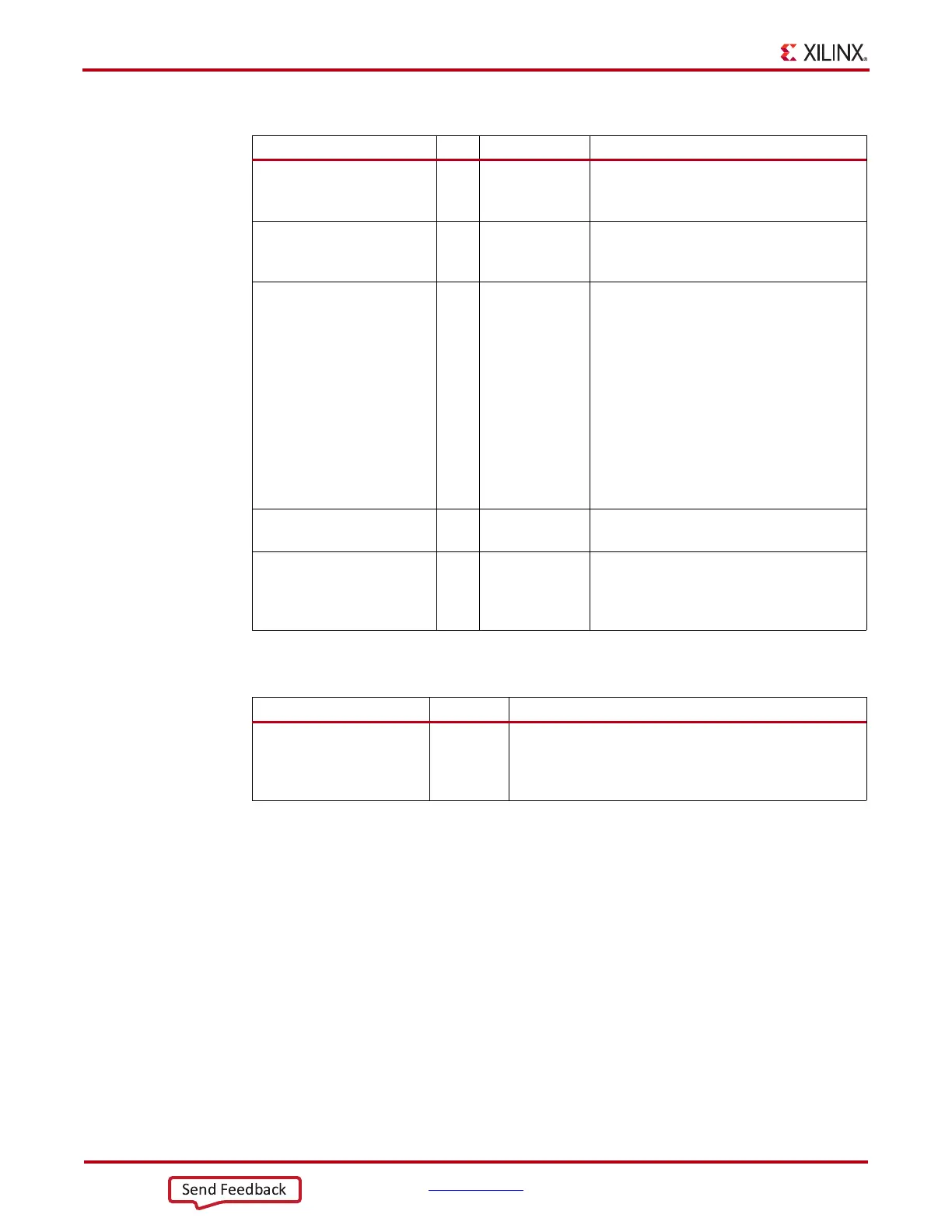

Table 3-4: FPGA TX Interface Ports

Port Dir Clock Domain Description

TXCHARDISPMODE[3:0] In TXUSRCLK2 When 8B/10B encoding is disabled,

TXCHARDISPMODE is used to extend the

data bus for 20- and 40-bit TX interfaces.

TXCHARDISPVAL[3:0] In TXUSRCLK2 When 8B/10B encoding is disabled,

TXCHARDISPVAL is used to extend the

data bus for 20- and 40-bit TX interfaces.

TXDATA[31:0] In TXUSRCLK2 The bus for transmitting data. The width of

this port depends on TX_DATA_WIDTH:

TX_DATA_WIDTH = 16, 20:

TXDATA[15:0] = 16 bits wide

TX_DATA_WIDTH = 32, 40:

TXDATA[31:0] = 32 bits wide

When a 20-bit or 40-bit bus is required, the

TXCHARDISPVAL and

TXCHARDISPMODE ports from the 8B/

10B encoder is concatenated with the

TXDATA port. See Table 3-2, page 77.

TXUSRCLK In Clock This port is used to provide a clock for the

internal TX PCS datapath.

TXUSRCLK2 In Clock This port is used to synchronize the FPGA

logic with the TX interface. This clock must

be positive-edge aligned to TXUSRCLK

when TXUSRCLK is provided by the user.

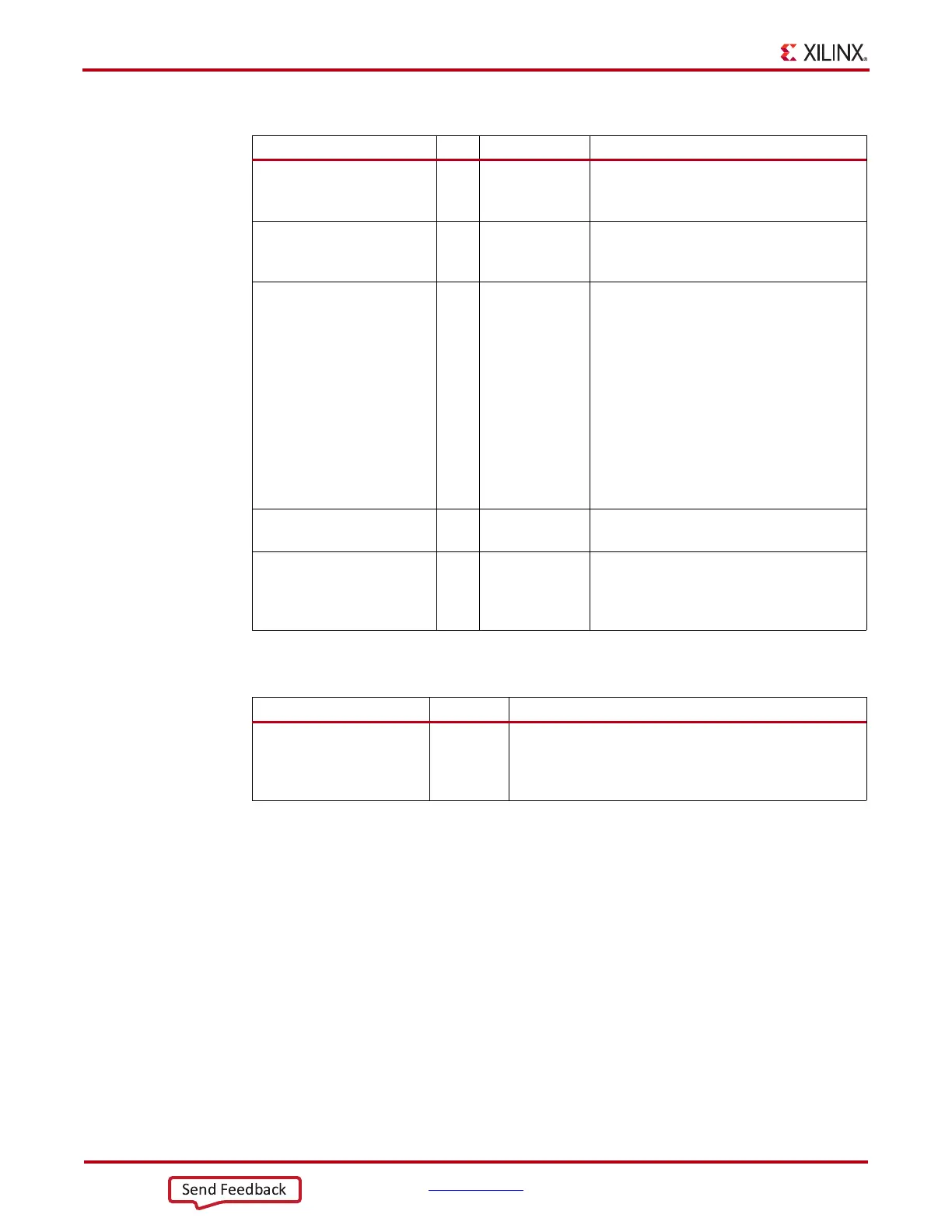

Table 3-5: FPGA TX Interface Attributes

Attribute Type Description

TX_DATA_WIDTH Integer Sets the bit width of the TXDATA port. When 8B/10B

encoding is enabled, TX_DATA_WIDTH must be set to 20

or 40. Valid settings are 16, 20, 32, and 40. See Interface

Width Configuration, page 76 for more information.

Loading...

Loading...