70 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 2: Shared Features

Digital Monitor

Functional Description

The receiver uses an adaptive algorithm in optimizing a link. The digital monitor provides visibility

into the convergence state of these adaptation loops. The digital monitor requires a clock;

RXUSRCLK2 can be used for this. The select line on which adaptation loops to monitor is

controlled through the RX_DEBUG_CFG attribute. The output port DMONITOROUT contains the

convergence code(s) for a selected loop. All loops are continuous. A continuous loop has three

possible convergence states: min, max, or dithering.

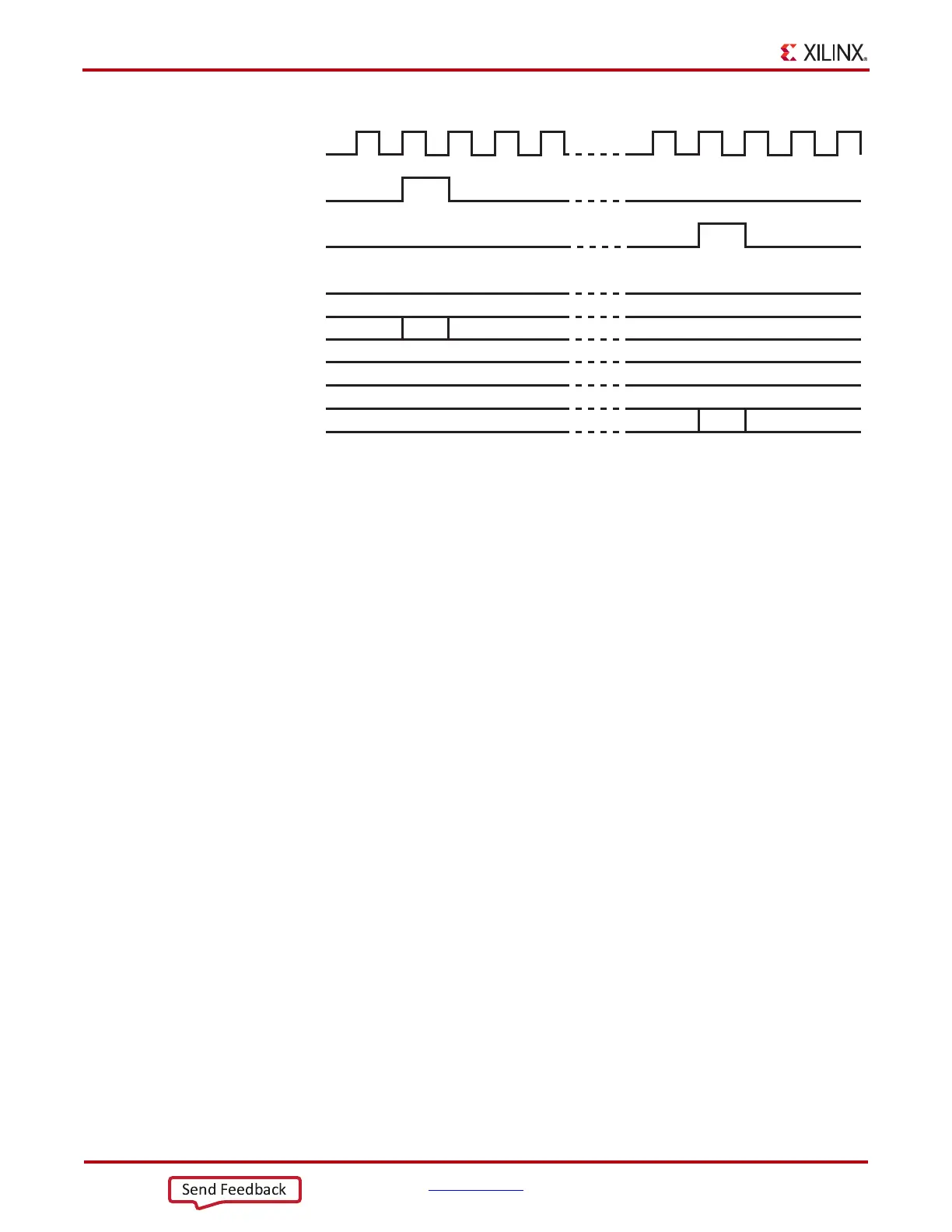

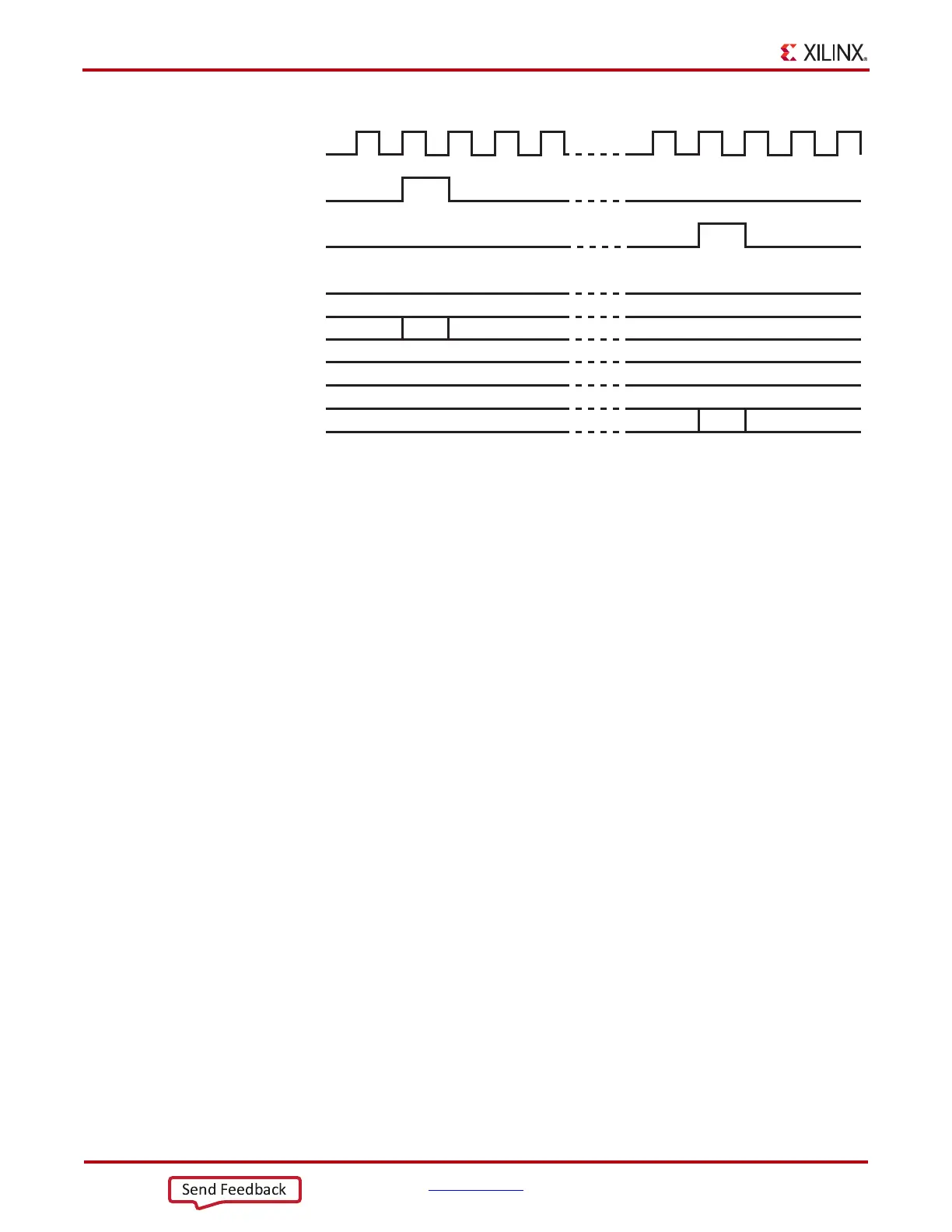

X-Ref Target - Figure 2-24

Figure 2-24: DRP Read Timing

UG482_c2_13_040213

(1)

(1) After a DRP read is requested, it takes:

- R/W registers: 5 DRPCLK clock cycles for the DRPRDY signal to be asserted.

- Read-only registers: Ceiling((DRPCLK freq/USRCLK freq)*6)+7 DRPCLK clock cycles for the

DRPRDY signal to be asserted. The duration depends on the ratio between the DRP clock

frequency and the USRCLK clock frequency.

DRPCLK

DRPEN

DRPRDY

DRPWE

DRPADDR

DRPDI

DRPDO

ADR

DAT

Loading...

Loading...