7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 71

UG482 (v1.9) December 19, 2016

Digital Monitor

Ports and Attributes

Table 2-31 shows the digital monitor ports.

Table 2-32 shows the digital monitor attributes.

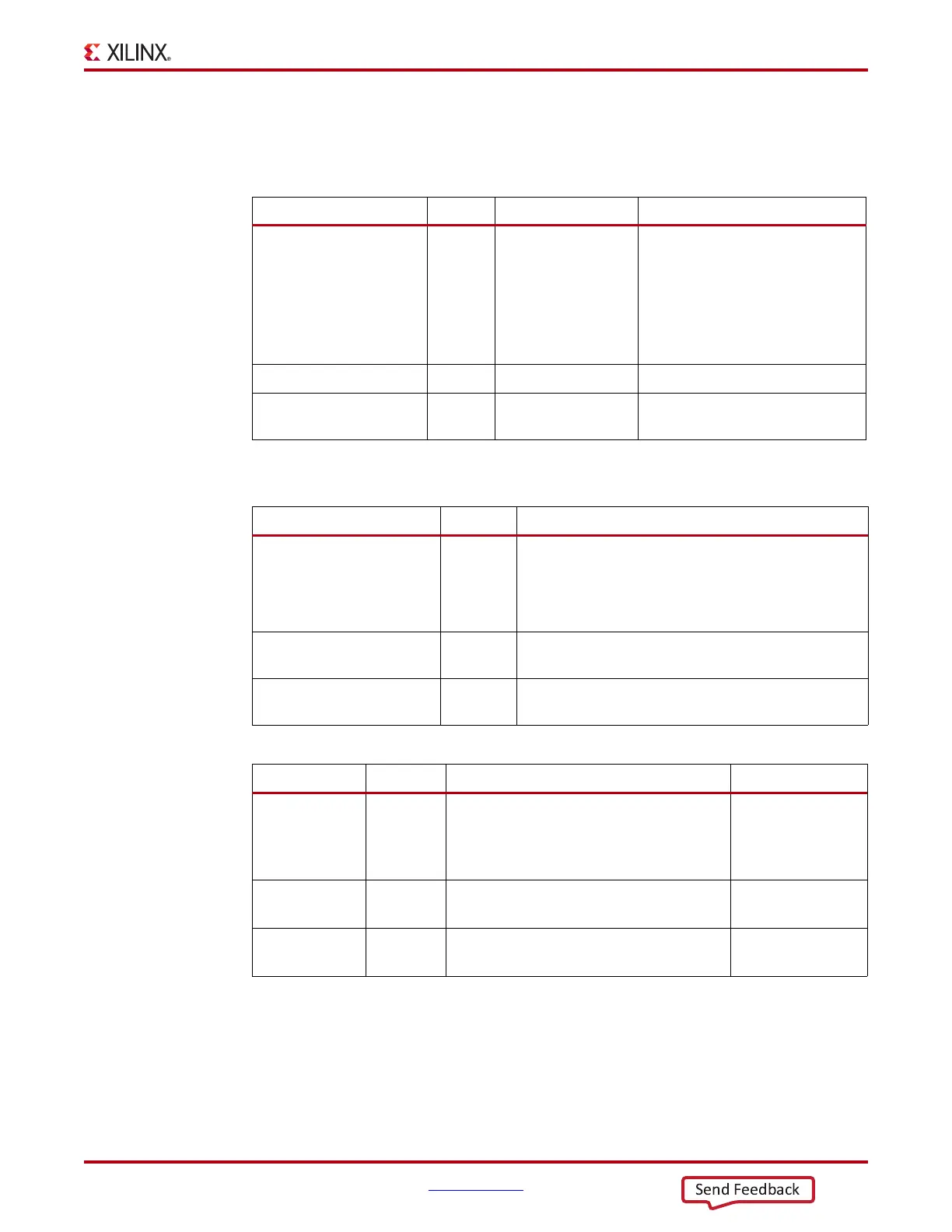

Table 2-31: Digital Monitor Ports

Port Dir Clock Domain Description

DMONITOROUT[14:0] Out Async/Local Clock Digital Monitor Output Bus:

• [14:8] Unused

• [7] - Internal Clock

Adaptation loops:

• [6:0] RXOS

• [6:3] RXLPMHF, RXLPMLF

DMONITORCLK In Async Digital monitor clock

DMONFIFORESET In DMONITORCLK Reserved. Tie To GND. Reset use

for sync mode operation.

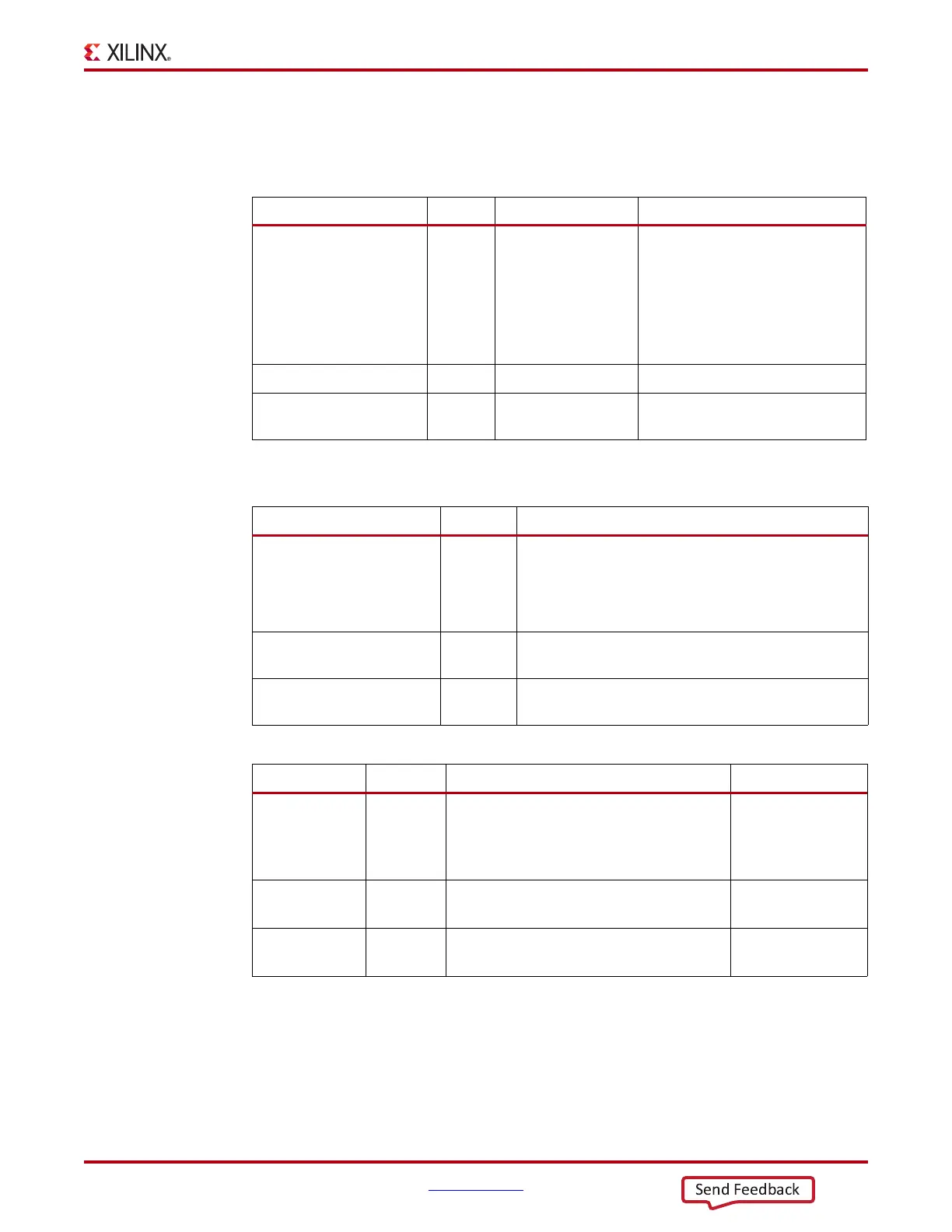

Table 2-32: Digital Monitor Attributes

Attribute Type Description

RX_DEBUG_CFG[13:0] 14-bit

Binary

[13:8] - Reserved. Set to 6'h00

[7:6] - Reserved. Set to 2’b11.

[5] - Reserved. Set to 1’b0.

[4:0] - Select adaptation loop: See

Table 2-33.

CFOK_CFG[42] 1-bit

Binary

Reserved. Set to 1'b1.

DMONITOR_CFG[23:0] 24-bit

Binary

Reserved. Set to 24'h008101.

Table 2-33: Select Adaptation Loop Description Details

DRP Address DRP DI Loop Description Code Mapping

0x0A5 0x00C2

RXLPMOS -Base line wander cancellation

7-bit signed with double neutral

7'd0 - min (neg)

7'63 - neutral

7'64 - neutral

7'127 - max (pos)

0x0A5 0x00C3

RXLPMHF - LPM high-frequency gain 4'd0 - min

4'd15 - max

0x0A5 0x00C4 RXLPMLF - LPM low-frequency gain

4'd0 - min

4'd15 - max

Loading...

Loading...