190 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

The content of the RX elastic buffer becomes invalid if an RX elastic buffer overflow or underflow

condition occurs. When any of these conditions occur, the RX elastic buffer should be reset and

reinitialized by using GTRXRESET, RXPCSRESET, RXBUFRESET, or the GTP transceiver

internally generated RX elastic buffer reset. The internally generated RX elastic buffer reset can

occur on channel bonding change, comma realignment, electrical idle, or rate change conditions.

The RX elastic buffer is also used for clock correction (see RX Clock Correction) and channel

bonding (see RX Channel Bonding, page 198). Clock correction is used in cases where XCLK and

RXUSRCLK are not frequency matched. Table 4-35 lists common clock configurations and shows

whether they require clock correction.

When the RX elastic buffer is used, the setting of CLK_COR_MIN_LAT affects the latency through

the buffer, regardless of whether clock correction is used.

RX Clock Correction

Functional Description

The RX elastic buffer is designed to bridge between two different clock domains, RXUSRCLK and

XCLK, which is the recovered clock from CDR. Even if RXUSRCLK and XCLK are running at

same clock frequency, there is always a small frequency difference. Because XCLK and

RXUSRCLK are not exactly the same, the difference can be accumulated to cause the RX elastic

buffer to eventually overflow or underflow unless it is corrected. To allow correction, each GTP

transceiver TX periodically transmits one or more special characters that the GTP transceiver RX is

allowed to remove or replicate in the RX elastic buffer as necessary. By removing characters when

the RX elastic buffer is too full and replicating characters when the RX elastic buffer is too empty,

the receiver can prevent overflow or underflow.

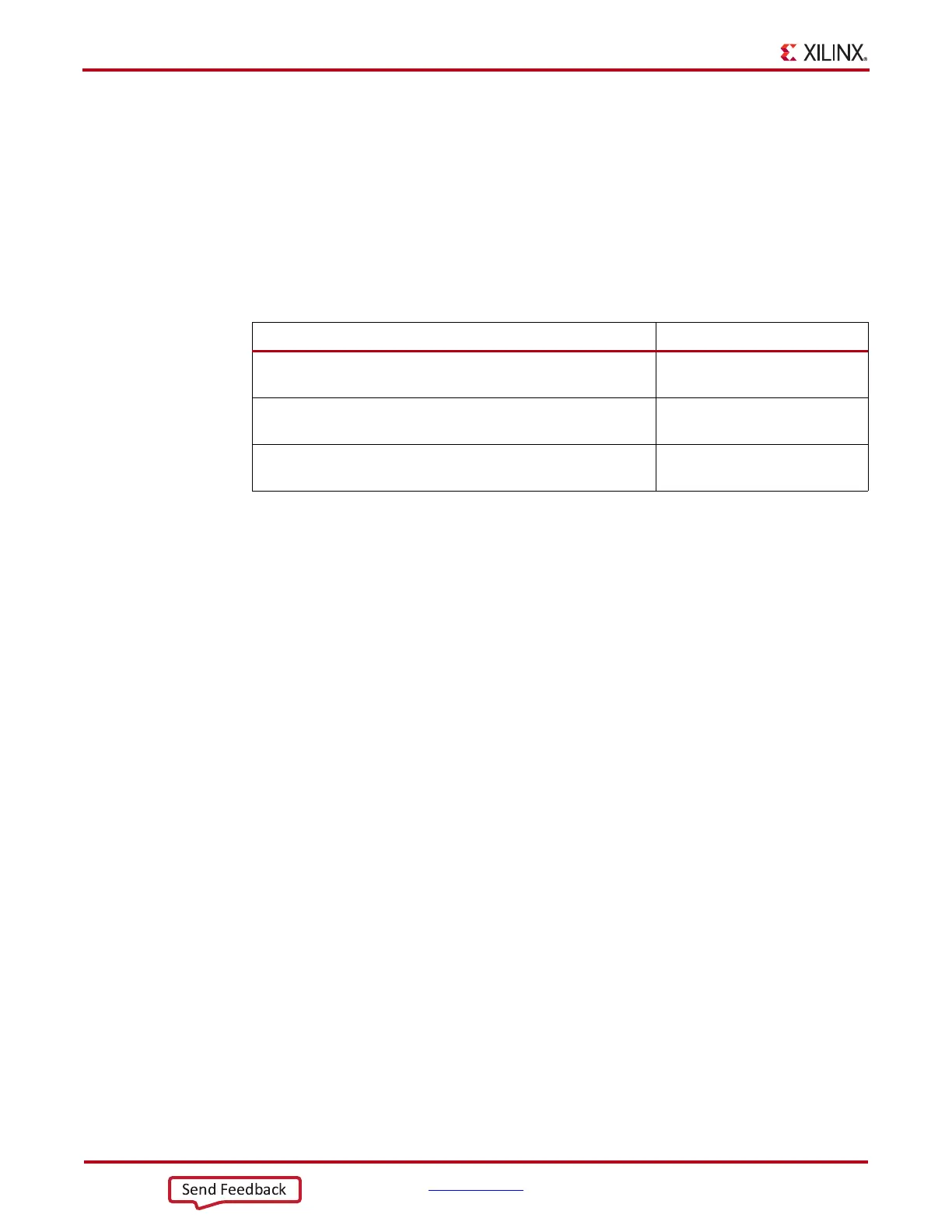

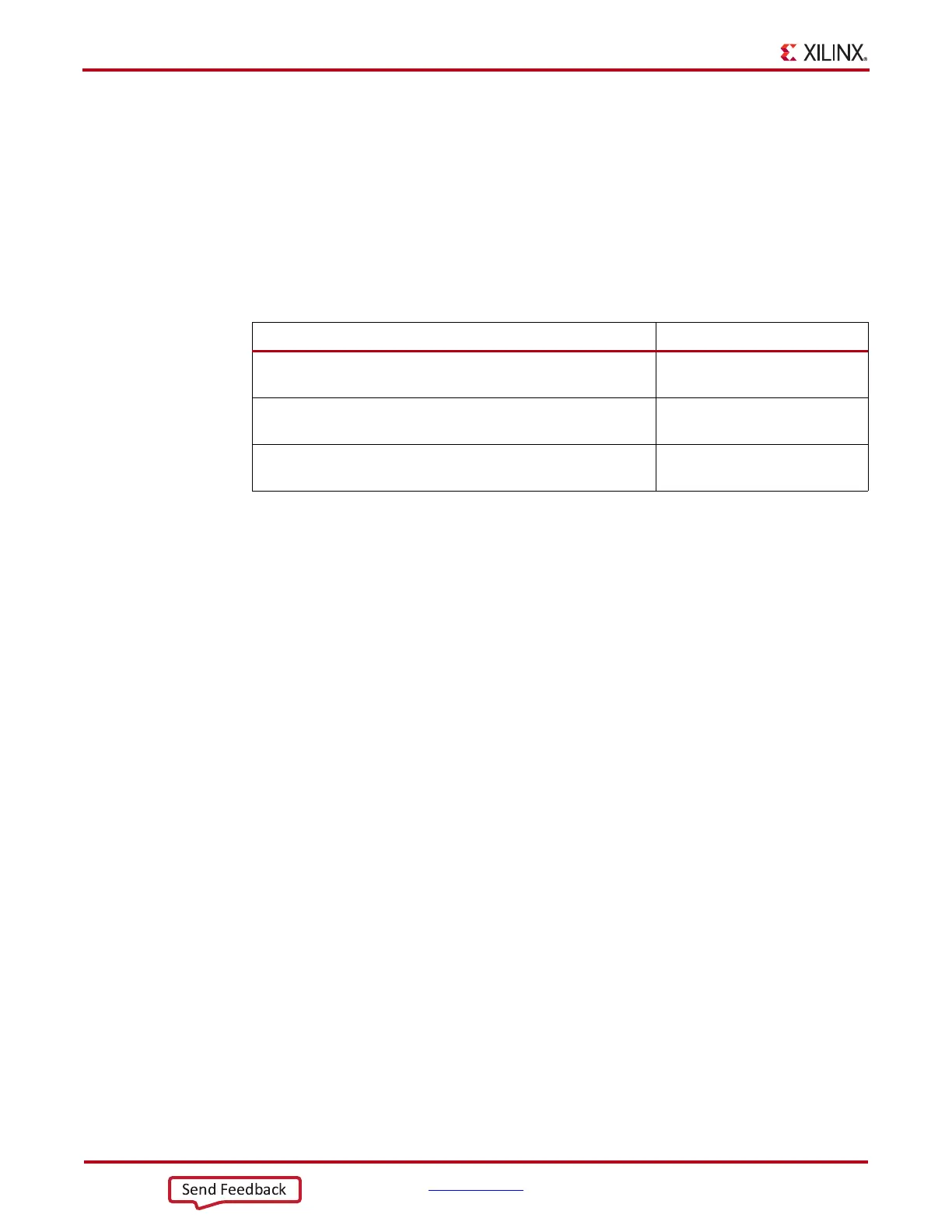

Table 4-35: Common Clock Configurations

Types of Clocking Require Clock Correction?

Synchronous system where both sides uses the reference clock

from the same physical oscillator.

No

Asynchronous system when separate reference clocks are used and

the GTP transceiver receiver uses an RX recovered clock.

No

Asynchronous system when separate reference clocks are used and

the GTP transceiver receiver uses a local clock.

Yes

Loading...

Loading...