186 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

It is necessary to start the RX phase alignment after RX CDR is locked to ensure that the RX

recovered clock and RXUSRCLK are stable and ready to be used for alignment.

When the RX elastic buffer is bypassed, data received from the PMA can be distorted due to phase

differences after conditions such as a GTP transceiver reset or rate change. If the received data

evaluated at the fabric interface is invalid on any lane, the RX alignment procedure needs to be

repeated for the interface after RX CDR is locked on all lanes.

RX Elastic Buffer

Functional Description

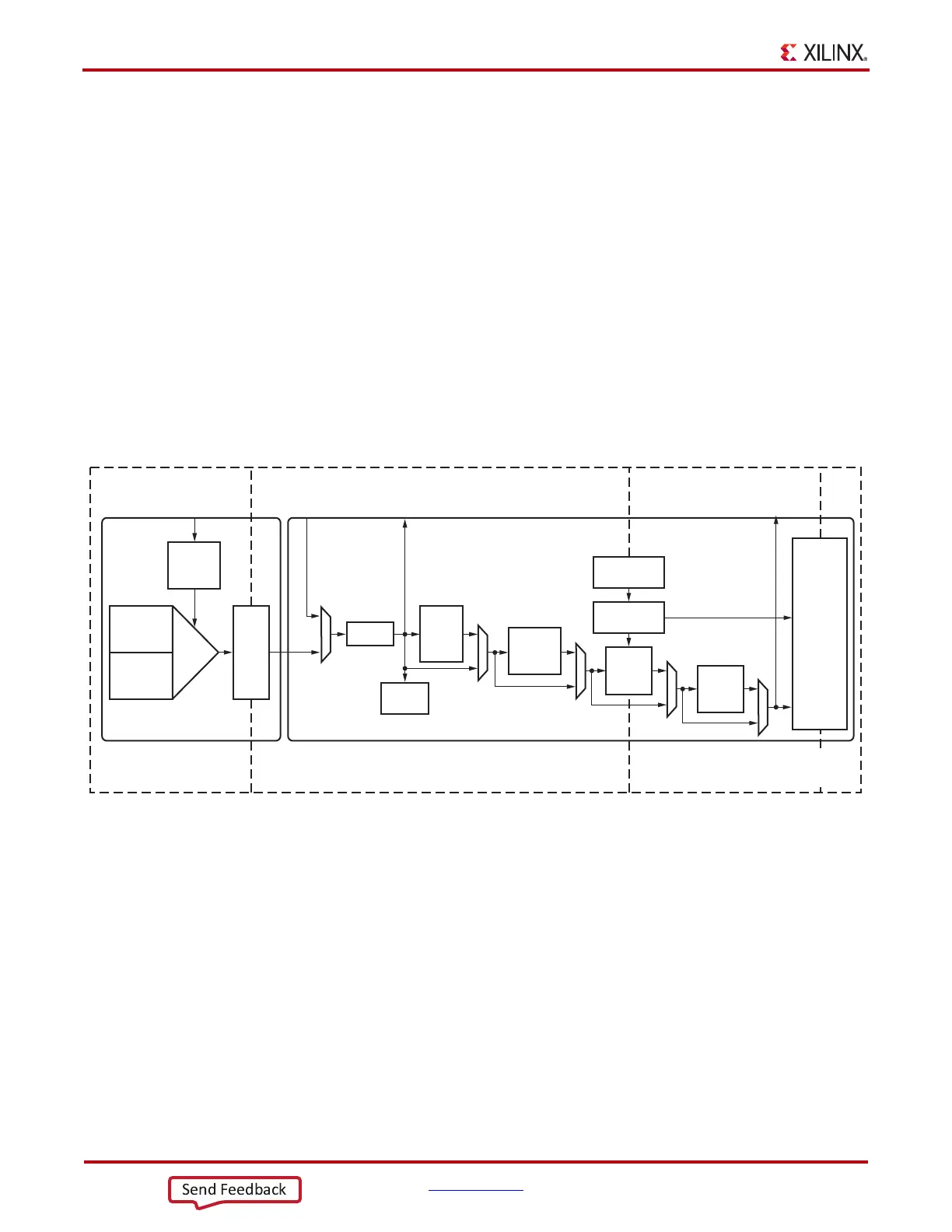

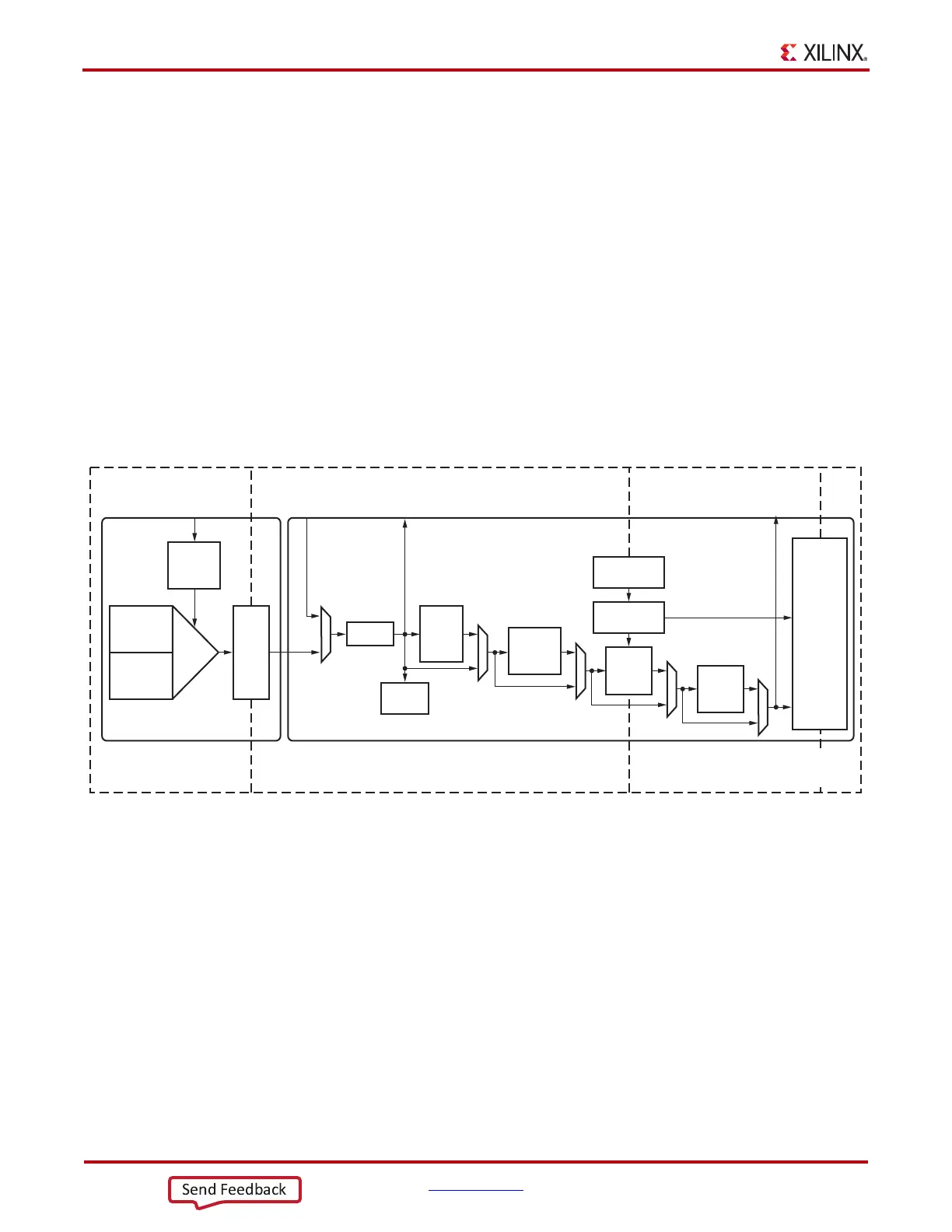

The GTP transceiver RX datapath has two internal parallel clock domains used in the PCS: The

PMA parallel clock domain (XCLK) and the RXUSRCLK domain. To receive data, the PMA

parallel rate must be sufficiently close to the RXUSRCLK rate, and all phase differences between

the two domains must be resolved. Figure 4-43 shows the two parallel clock domains: XCLK and

RXUSRCLK.

The GTP transceiver includes an RX elastic buffer to resolve differences between the XCLK and

RXUSRCLK domains. The phase of the two domains can also be matched by using the RX

recovered clock from the transceiver to drive RXUSRCLK and adjusting its phase to match XCLK

when the RX buffer is bypassed (see RX Buffer Bypass, page 174). All RX datapaths must use one

of these approaches. The costs and benefits of each approach are shown in Table 4-32.

X-Ref Target - Figure 4-43

Figure 4-43: RX Clock Domains

Clock from

PLL0 or PLL1

From TX Parallel

Data (Near-End

PCS Loopback)

To TX Parallel

Data (Far-End

PMA Loopback)

To TX Parallel

Data (Far-End PCS

Loopback)

FPGA Parallel

Clock

(RXUSRCLK2)

PCS Parallel

Clock

(RXUSRCLK)

PMA Parallel

Clock

(XCLK)

RX Serial

Clock

RX EQ

RX

Clock

Dividers

SIPO

RX OOB

Polarity

PRBS

Checker

Comma

Detect

and

Align

RX

Gearbox

FPGA RX

Interface

8B/10B

Decoder

RX

Elastic

Buffer

RX PIPE

Control

RX Status

Control

UG482_c4_25_112911

RX CDR

Loading...

Loading...